8月16日消息,消息源 Digitime 昨日(8月15日)發布博文,報道稱臺積電持續推進先進封裝技術,正式整合CoWoS與FOPLP,推出新一代“CoPoS”工藝。

首條CoPoS實驗線將于2026年設立,量產預計落地嘉義AP7廠與美國亞利桑那州廠,最快2028年底至2029年上半年量產。

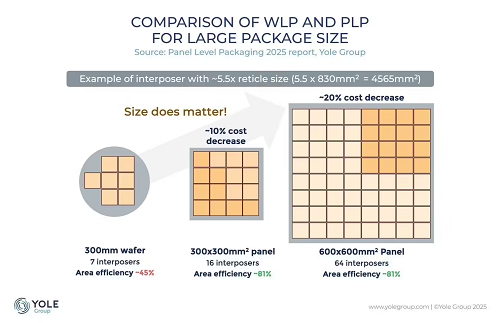

消息稱CoPoS本質上是CoWoS的面板化升級,將芯片排列在大型方形基板上,取代傳統圓形硅中介層,不僅能有效提升產能,還能大幅優化面積利用率與成本。

CoPoS技術針對AI大尺寸芯片的封裝挑戰,創新采用玻璃或藍寶石方形載具作為中介層,并在其上鍍制RDL(再分布層),支持更大光罩和更高集成度,有效緩解芯片尺寸擴大帶來的翹曲(warpage)問題。

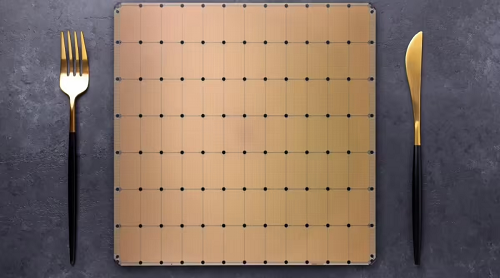

面板尺寸可達310x310mm、515x510mm甚至750x620mm,遠超傳統300mm圓形晶圓,為AI芯片擴產和降低單位成本提供了技術支撐。

據半導體供應鏈消息,臺積電已規劃于2026年在采鈺(臺積電子公司)設立首條CoPoS實驗線,而嘉義AP7廠的P4、P5廠則將作為量產據點,最快2028年底至2029年上半年實現量產。此外,臺積在美國亞利桑那州也同步規劃兩座先進封裝廠,分別以SoIC與CoPoS為主。

隨著相關設備規格與訂單量確定,全球供應鏈企業紛紛加入競標行列,首波供應鏈名單囊括KLA、TEL、Screen、Applied Materials、Disco等國際大廠,以及印能、辛耘、弘塑、均華、致茂、志圣等 13 家臺廠。

簡要介紹下不同封裝工藝:

· CoWoS(Chip-on-Wafer-on-Substrate)是臺積電主力封裝技術,將芯片排列在圓形硅中介層,適用于高性能計算芯片

· FOPLP(Fan-Out Panel Level Packaging)是扇出型面板級封裝技術,可在更大面板上進行芯片封裝;

· CoPoS(Chip-on-Panel-on-Substrate)是臺積電新一代先進封裝技術,將芯片排列于方形面板基板,提升產能、降低成本,并解決大尺寸芯片封裝難題。

· WMCM(Wafer-level Multi-Chip Module):臺積電升級版 InFO-PoP 封裝技術,專為蘋果等高端客戶開發。

· SoIC(System on Integrated Chips):臺積電 3D 堆疊型封裝技術,實現高密度集成與互聯。