摘要:本文目標是根據航天電子設計的需要,提出一種高可靠性微處理器設計的設計方案。在分析了單粒子效應的和總結了高可靠性設計技術的基礎上,對 oregano systems公司提供的 mc8051IP軟核進行了修改。修改后的 IP核滿足設計要求,運行穩定,最終實驗結果說明:設計方案合理,實現簡單,具備實用價值。

引言

隨著我國航天事業的發展,高密度集成電路器件在航天器的研制中被大量使用,然而隨著器件集成度的提高和工作電壓的降低,空間輻射環境對電子系統的影響越來越多。空間輻射環境對電子系統的損害最主要的是單粒子效應(Single Event Effect) ,它們會使器件失效或者工作狀態發生改變,影響電子設備的可靠運行 5。基于筆者所在單位承擔的大量航天工程任務中關鍵部位均使用了 8051微控制器,本文根據航天電子設計的要求對一款8051IP軟核進行了修改,以適應航天設備的需要。

1 mc8051IP核介紹

IP(Intellectual Property)原意指知識產權,在 IC設計領域則是指預先設計實現某種功能的模塊。IP核(IP模塊)則是指完成某種功能的虛擬電路模塊,也稱之為虛擬部件。

根據 IP的提供方式通常把 IP核分為硬 IP(硬核 Hard Core)、軟 IP(軟核 Soft Core)和固 IP(固核 Firm Core )。

硬核是針對某個特定工藝的一套物理版圖,電路布局布線和工藝是確定的,已經過樣品電路的驗證。硬核的優點是它的高速度和安全性,但由于依賴特定的工藝,所以缺少靈活性。

軟核是用硬件描述語言(Verilog HDL或 VHDL)的形式描述功能塊的行為,但是并不涉及用什么電路和電路元件實現這些行為。軟核具有的特點是可以根據用戶需要靈活的進行修改定制。

固核是一種介于軟核和硬核之間的 IP核,通常以 RTL代碼和對應具體工程網表的混合形式提供。固核是完成了綜合的功能塊,有較大的設計深度,通常以網表的形式提交客戶。

mc8051IPcore是 Oreganosystems公司提供的一個應用廣泛的開源 8051IP軟核。

它由算術運算單元,定時器 /計數器,串口,內部 ram,外部 ram及 rom組成。mc8051_alu為運算單元,由加法器,乘法器,除法器等基本運算單元組成。mc8051_control為 mc8051的控制通路。包括有特殊寄存器,譯碼單元,多路選擇器,中斷及指令狀態機等基本功能。2抗單粒子可靠性設計技術

可靠性設計的基本原理是冗余,包括信息冗余,時間冗余等。目前抗單粒子效應的設計技術中應用最廣的技術有三模冗余(Triple Modular Redundance ,TMR),檢錯糾錯(Error Detection And Correction ,EDAC) 1基于軟件的控制流檢測

2。本文主要采用前2種可靠性設計方法。

2.1 三模冗余(TMR)介紹

三模冗余是指將目標部件復制相成同的三個目標部件來實現一個目標部件的功能,三個目標部件最終將通過一個判決器來判斷目標部件的正確狀態。它利用的是相同一組部件同時出現錯誤概率較小的原理來實現可靠性的提高。

TMR可用于各種IP設計的各階段,既可以在系統級進行冗余,也可以是局部冗余。

2.2 糾錯檢錯(EDAC)

2.2.1 EDAC概述

EDAC可以用來檢測電子設備中由SEU引起的存儲為翻轉錯誤。EDAC的基本結構包括3個部分:編碼模塊,解碼模塊,存儲模塊。其中EDAC 編碼模塊將需要處理的數據進行相關算法的編碼,產生校驗碼,與待處理數據一同存入存儲模塊。數據需要讀出的時候,EDAC解碼模塊將數據與相應校驗碼進行解碼處理,得出正確結構。編碼與解碼所采用的編碼方式可以根據需要選擇,如漢明碼,最佳奇權碼,藤原英二碼等等。

2.2.2 漢明碼介紹

下面以擴展漢明碼為例說明編碼糾錯檢錯的原理。 擴展漢明碼(Extended Hamming Code)在存儲系統的糾錯檢錯中得到了廣泛應用。他的最小碼距是4,對于數據位數 k,校驗位數 r,他們之間的關系需滿足 2r-1 ≥ k+r。如果數據位 k增加一倍,校驗位 r也只需要增加1位,所以它具有相當高的編碼效率。 8位數據經過4位編碼后的數據結構如下:

C= [D7D6D5D4D3D2D1D0C3C2C1C0]其中 D7~D0是數據位,C3~C0是校驗位:

C3= D7 ⊕D6 ⊕ D5 ⊕ D4 ; C2= D7 ⊕D3 ⊕ D2 ⊕ D1; C1= D6 ⊕D5 ⊕ D3 ⊕ D2 ⊕ D0 ; C0= D6 ⊕D4 ⊕ D3 ⊕ D1⊕ D0

解碼時需計算存儲數據的伴隨向量 S: S3= C3 ⊕CB3;S2= C2 ⊕CB2 ;S1= C1⊕CB1;S0= C0 ⊕CB0 其中 CB0,CB1,CB2,CB3為 8位數據在解碼時刻的校驗位。根據算得的伴隨向量 S我們就可以判斷數據位是否發生錯誤及錯誤發生的位置。

2.3 兩種糾錯方法的比較

TMR與 EDAC都屬于硬件冗余,對于不同字長的存儲器,他們所占用的面積開銷和時間開銷是不同的。TMR所占用的面積開銷包括冗余的2個目標器件以及判決器及附屬電路邏輯,EDAC所增加的面積開銷則包括了增加的校驗位,編碼器,解碼器及附屬邏輯 1。根據以上分析我們可以得出結論,對于保護寄存器,寄存器組等容量較小的存儲器件,TMR有實現簡單,增加面積較少的有點。而對于大容量的存儲器,則應當采用 EDAC來進行糾錯檢錯。

3高可靠性 8051具體方案設計及實現通過對 SEU的機理分析及 mc8051結構分析可以得出,容易受到粒子輻射的關鍵部位有

3:特殊寄存器(Special Function Register ,SFR),內部 ram,外部 ram。本論文就上述三個模塊對 mc8051IP核進行了該進。

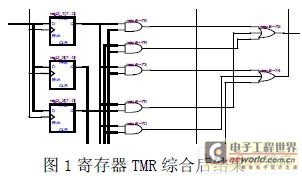

3.1特殊寄存器(SFR)

mc8051IP核的特殊寄存器(SFR)均在 control_mem文件中實現。該模塊實現 8051譯碼功能。SFR字節地址范圍是80H-FFH,他們在 RAM中并不是完全連續的,21個 SFR離散的分布在上述字節區域的128個字節單元中。在mc8051IP核中并沒用將這些SFR設計在內部 ram中,而是對應地址分別實現的。對 SFR的加固處理是采用了 TMR技術。具體實現步驟如下:

綜合后結果截取如下圖:

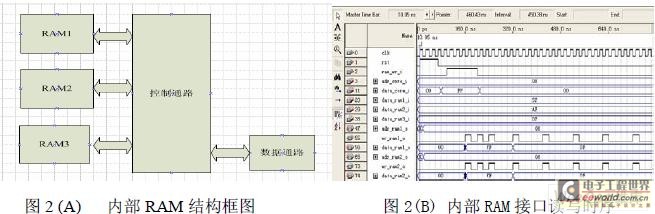

3.2內部 RAM

該 IP核可支持 128字節內部RAM.由 2.3分析,方案采用 TMR方式對內部 RAM進行處理,選用 3個相同的 128字節的 RAM作為冗余的存儲器,由 mc8051_ram_fsm與 mc8051_ram_dataflow兩個模塊組成了內部 RAM的數據通路,其中前者完成寫優先的讀寫狀態控制,后者完成數據流向控制。數據通路負責完成數據校驗。控制通路與數據通路組成內部 RAM接口邏輯。經過仿真后內部 RAM接口結構框圖及讀寫時序如下:

圖 2(B)可看出:寫數據時,數據輸入后第二個周期被寫入RAM;讀數據時,讀指令被檢測到后的第 5個周期經校驗后的正確數據被輸出并且被回寫給RAM。在接入工程應用時需將外部時鐘進行 6倍頻以配合 cpu讀寫時序。

3.3 外部 RAM

外部 RAM最大可以支持64K,同樣由 2.3分析,方案選取能糾 1位錯檢 2位錯的擴展漢明碼進行 EDAC處理。其中,數據處理單元完成數據的編碼,解碼,地址鎖存及數據輸出功能。讀寫狀態機 FSM完成外部 RAM的讀寫狀態控制,同樣,為配合 ram的 IP軟核時序,我們將 FSM設計為寫優先。仿真后的 EDAC結構框圖及讀寫時序如下:

需要指明的時上圖仿真時外部時鐘為 10Mhz,經過 altera公司 alt_pll進行了 6倍頻及相位調整,前一個寫指令未被執行的原因是 PLL需要 2到 3個時鐘周期的調整穩定頻率輸出。 EDAC模塊的讀寫時序與內部 RAM相似,寫數據時第 2個時鐘周期經過處理后的 8位原數據以及 4位校驗數據一同被寫進 RAM,讀數據時,讀出的 12位數據經過解碼糾正后在第 5個時鐘周期輸出 8位數據并將糾正后的 12位數據回寫進 RAM,以防止 SEE的積累。由時序圖可知以上設計完全符合設計要求。

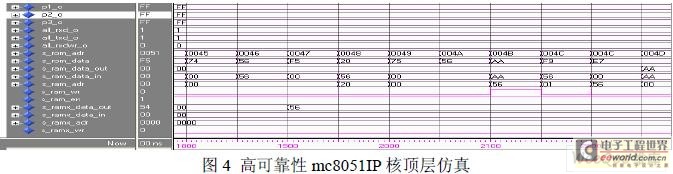

3.4全系統仿真

在完成上述幾個方面的 IP定修改之后,對 mc8051的頂層系統進行了 modelsim的綜合前仿真,仿真部分結果如下:

仿真時將 ROM的初始化文件設置為 mc8051文檔中的 tc1.hex,方便與原 IP核進行對照。為在 modelsim仿真前,我們已將 altera的 altera_mf庫加入到 modelsim庫文件中。在進行功能仿真的時候調用了其中的 alt_pll來進行時鐘處理。在使用該 IP核時可以根據具體采用的器件來完成倍頻的功能。以上時序完全正確,說明修改后的 IP核與原 IP核功能上等同。

4結論

本文在oreganosystems公司提供的開源mc8051IP軟核的基礎上根據高可靠性航天電子設計的方法修改了部分模塊,實踐證明修改后的功能與原 mc8051IP 核完全相同,達到設計目的。可以根據需要將 IP核綜合后生成的網表文件下載進現場可編程邏輯器件( FPGA)或者進行流片設計成 ASIC,具備航天使用價值。本文創新點:本文根據在研航天項目需要,定制了一種可適應航天工作環境的微控制器 IP核。采用常用的容錯技術對普通商用 IP核進行了加固。該 IP核的成功改造,可以一定程度上減輕我國軍品級芯片對國外的依賴,提高了效率,為后續的研究積累了寶貴經驗。