電荷耦合器件(Charge Coupled Devices,簡稱CCD)是一種光電轉換式圖像傳感器。它利用光電轉換原理將圖像信息直接轉換成電信號,實現非電量測量。由于CCD的輸出信號是負極性的離散模擬信號,并且混雜有幅度較大的復位脈沖干擾,為了獲得高質量信號,必須對CCD輸出信號進行直流箝位、相關雙采樣、低通濾波和放大等預處理,以消除各種干擾和噪聲。同時,為了便于計算機處理和大容量存儲,還必須對CCD輸出信號進行數字化處理。目前市場上CCD專用的視頻信號處理器件不僅具有雙采樣技術,而且還具有自動暗電平補償、自動增益和A/D轉換等功能。這里給出了一款CCD專用的視頻信號處理器件XRD44L60,并介紹了基于VHDL 的XRD44L60CPLD邏輯控制電路。

2 XRD44L60簡介

XRD44L60是Exar公司CCD專用的視頻信號處理器件。該器件是針對CCD影像應用產品而設計的。XRD44L60采用相關雙采樣 (Correlated Double Sampling,簡稱CDS)技術提取圖像信息,可編程增益(Programmable Gain Amplifier,簡稱PGA)控制范圍可達6 dB+38 dB,具有良好的輸人信號箝位和CDS輸入偏移校正性能,并提供暗電平箝位,給出準確的暗電平參考。XRD44L60還有一個10位A/D轉換器,轉換速率高達16 MHz,便于CCD陣列信號的數字處理。此外,XRD4-4L60的串行接口包括一個10位的移位寄存器和多個并行寄存器,可用于編程設置其工作參數。 XRD44L60的電源電壓為3.0 V,功率為120 mW,適用于小型化嵌入式CCD數字相機系統。

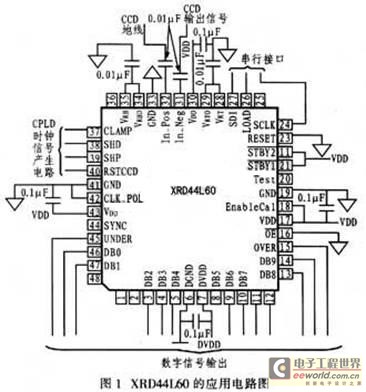

3系統電路設計

XRD44L60硬件電路設計如圖1所示。其中,In_Pos和In_Neg為模擬信號輸入端口,用于連接CCD的輸出信號。CLAMP,SHD,SHP 及RSTCCD為時鐘信號控制引腳,用于連接CPLD信號的輸出端,以控制器件工作。LOAD,SDI,SCLK為串行接口可編程設置XRD44L60的工作參數。DB0~DB9為10位數字信號輸出,可與信號處理單元連接。

4 XRD44L60的時序控制

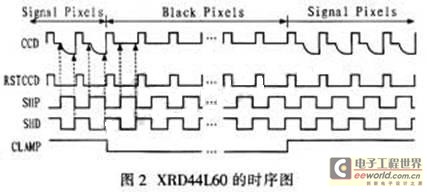

采用可編程邏輯器件(CPLD)技術和VHDL語言實現對CCD視頻信號處理器件XRD44L60的控制,使其完成CCD視頻信號的放大、噪聲處理及數字化,并輸出對應的數字信號。XRD44L60的工作時序需要根據具體的CCD器件來確定。下面以TCD1501D型CCD為例,介紹XRD44L60的工作時序。TCD1501D的工作頻率為1 MHz,CCD輸出信號周期為2μs,其外部時鐘輸入由有源晶體振蕩器提供,頻率為8 MHz。當CLK_POL為低電平時,XRD44L60的時序如圖2所示。驅動脈沖包括CCD復位脈沖RSTCCD、相關雙采樣暗電平時鐘SHP、相關雙采樣信號電平時鐘SHD、相關雙采樣箝位控制脈沖CLAMP。

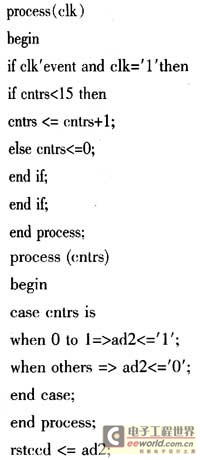

4.1 RSTCCD脈沖的產生

由圖2可知,RSTCCD的周期為2μs,占空比為1:7。因此,可對輸入時鐘脈沖16分頻,其高電平占2個周期的時鐘脈沖;低電平占14個周期的時鐘脈沖。當計數器計數到15時,計數器清零,重新計數,相關程序源代碼如下:

4.2 SHD和SHP脈沖的產生

由圖2判斷出,SHD和SHP的周期均為2μs,占空比為1:1。因此,可采用上述方法獲得這兩個脈沖。

4.3 CLAMP脈沖的產生

CLAMP脈沖由CCD的輸出決定,即當CCD的輸出信號為像元信號時,CLAMP為高電平;當CCD的輸出信號為暗像元信號時,CLAMP為低電平。

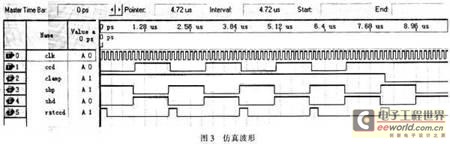

5驅動脈沖仿真波形

該沒計采用QuartusⅡ仿真軟件進行仿真。仿真波形如圖3所示。其中,CLK和CCD為輸入信號;CLAMP,SHD,SHP及RSTCCD為XRD44L60的驅動信號。

6 結語

基于VHDL的XRD44L60邏輯控制電路能夠產生滿足系統要求的驅動脈沖,整個系統設計能夠達到預期效果。將VHDL應用于XRD44L60時序電路設計,系統設計更簡單、靈活、可靠,因此可廣泛用于使用CCD的影像產品中。