Abstract:

Key words :

VITA46 VPX標準定義了一種通用尺寸的機箱,它可以容納各種形式的卡(參考文獻1)。這些卡插到一個通用背板上。本設計用PCIe的VITA46.4在一個VPX系統中的外設卡和主控制器之間傳送數據。它采用了PCIe Revision 1,工作速度為2.5Gbps。所有符合VPX的卡都必須使用自己的獨立時鐘,這與其它符合PCIe要求的系統不同,如PC。VPX外設卡也必須為PCIe事務建立自己的時鐘,這意味著,時鐘與主單板機是相位無關的。因此,外設時鐘是異步時鐘。PCIe標準允許這種情況,而對所有異步PCIe時鐘有嚴格的抖動容差要求。

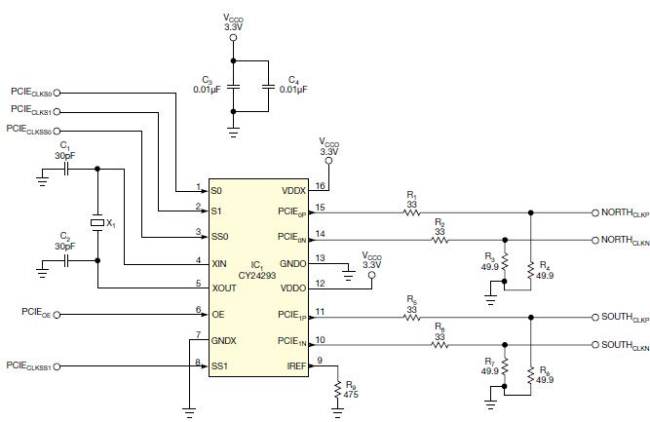

本設計中的外設卡使用了一片FPGA作為數字處理主器件。FPGA供應商的評估板通常采用PCIe接口,但板上不使用異步時鐘。為了實現異步時鐘, 可以用一只與某種型號振蕩晶體精確匹配的時鐘芯片(圖1)。時鐘芯片IC對晶體有抖動、老化和阻抗方面的要求。晶體應在-40°C~+85°C的溫度區間內保證這些要求。必須使用CY24293數據表中的公式計算晶體的負載電容值。來自CY24293的時鐘被直接送入FPGA的高速收發器時鐘引腳,從而獲得了外設卡與單板機之間可靠的PCIe分組傳輸。CY24293還有一些其它的元件與布局要求,它采用一種PCIe設備走線配置,要求有阻抗可控的特殊長度走線,以及特殊值的串聯電阻。

圖1,本電路將一個時鐘發生器輸出送至FPGA,獲得一個異步VPX時鐘

此內容為AET網站原創,未經授權禁止轉載。