基于速大容量存儲系統設計

西安電子科技大學 李華,王文英

摘要: 設計中相機輸出LVDS串行數據通過接收電平轉換和串并轉換后得到10路×8 bit的并行數據流,其數據流速率最大為66 MHz。之后根據相機MC1311的性能指標可計算出Camera Link高速接口與數據存儲系統的存儲容量要求與存儲速度要求,即:單幀數據量為1280×1024×8 bit;每秒最大數據量為500×1280×1024×8 bit;Camera Link高速接口單路數據速率為65.536 MByte,如果需要連續存儲60秒的視頻數據,則需要40 G Byte存儲器容量。100 GByte的存儲容量最多大約可存儲2.5分鐘視頻數據。

Abstract:

Key words :

在測量技術中,高速數字攝像機所拍攝到的大量數字圖像需要高速、大容量的圖像存儲設備來實時快速地存儲。用傳統的磁帶方式來記錄數據,其效率和安全性不高;靜態存儲器讀寫方便,但是存儲的數據會因斷電而丟失,所以不利于數據的長時間保存。而近幾年問世的閃存以其存儲容量大、體積小、可靠性高等優點,逐步向存儲系統進軍。

1 設計原理

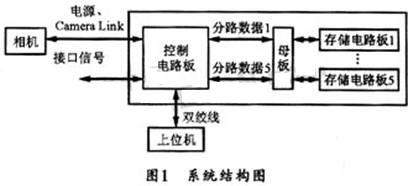

設計中相機輸出LVDS串行數據通過接收電平轉換和串并轉換后得到10路×8 bit的并行數據流,其數據流速率最大為66 MHz。之后根據相機MC1311的性能指標可計算出Camera Link高速接口與數據存儲系統的存儲容量要求與存儲速度要求,即:單幀數據量為1280×1024×8 bit;每秒最大數據量為500×1280×1024×8 bit;Camera Link高速接口單路數據速率為65.536 MByte,如果需要連續存儲60秒的視頻數據,則需要40 G Byte存儲器容量。100 GByte的存儲容量最多大約可存儲2.5分鐘視頻數據。圖1為系統結構圖。

2 核心器件選擇

設計中的存儲芯片采用SAMSUNG公司的NAND FLASH芯片K9 K8G08UOI,它的外部接口最高速度為40 MHz,接口寬度8位。每個芯片有8192塊,每塊有64頁,每頁大小為(2K+64)Bytes,其中64 Bytes為空閑區,存儲容量為8Gbit。它以頁為單位進行讀寫,以塊為單位進行擦除。控制核心FPGA采用ALTERA公司STRATIXⅡ系列的EP2S30F672I4,它有著豐富的觸發器和LUT,非常適合復雜時序邏輯的設計,具有1.3Mbit的內置存儲RAM,可以緩存一定量的數據。

3 系統設計

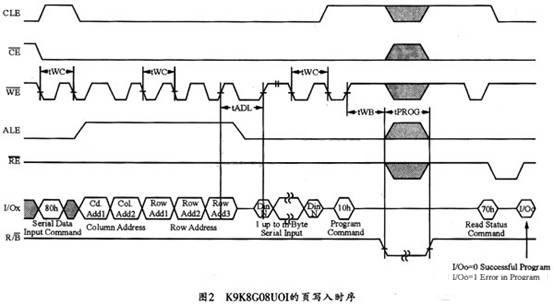

NAND Flash的數據存儲采用頁編程方式寫入,K9K8G08UOI的頁寫入時序如圖2所示。

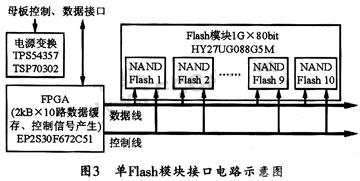

根據圖2的時序可以估算出單片K9K8G08UOI的數據存儲速率,其中tWC最小為25 ns,tADL為75ns,tWB為100 ns,tPROG為200μs。因此,寫入一頁所需時間大約為:200μs+100 ns+(2048+64) ×25ns+75 ns=252.975μs,由于一頁數據為(2K+64)B,所以單片K9K8G08UOI每Byte的數據存儲速率為:1/(252.975μs/(2048+64)B)=8.4152 MHz。可見單片K9K8G08UOI的寫入速度不能滿足Camera,Link的接口要求,故需用多片進行數據位擴展。為了解決NAND Hash存取數據速度較慢向題,可將相鄰10個8 bit視頻數據在FPGA內展寬為80 bit進行存取。而NAND Flash每Byte的存儲速率要求可降為6.6 MHz,故可滿足單片K9K8G08UOI的存儲速度要求。系統中每10片K9K8G08UOI組成一個1 G×80 bit的Flash模塊,共10個Flash模塊。每個Hash模塊共用一套控制線,數據線分別與FPGA相連。單Flash模塊的組成原理如圖3所示。

電路中Flash1~10的連接一致,即數據總線獨立連接到FPGA共用控制總線(帶驅動)。由圖3可見,若需要進一步降低單片Flash存儲速率,可進一步擴展Flash存儲器芯片數量。由于單片FPGA的I/O數有限,可將10個Flash模塊安排到5塊擴展存儲器板上,分別對應Camera Link串并轉換得到的一路數據(66 MHz×8 bit)。每個存儲器板與1片FPGA和2個Flash模塊相連后再分別與控制電路板上的FPGA相連來進行數據傳輸。其中的5塊擴展存儲器板采用相同結構。

4 FPGA邏輯設計

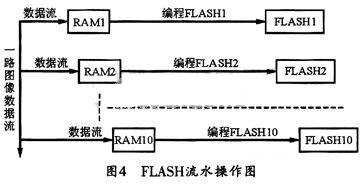

FLASH的基本操作分為兩個階段:加載時間和編程時間,寫入的時間瓶頸并不在加載時間,而是FLASH的編程時間。為了解決高速數據與低速FLASH之間的矛盾,可采用數據流串并轉換、多個模塊并行處理的方法。可在FPGA內部構建10個雙口RAM用來緩存數據,每個雙口RAM對應一個FLASH,相機過來的數據先緩存到RAM里,然后再寫到FLASH。數據寫到RAM可采用流水操作,數據寫滿第一個雙口RAM,接著寫第二個RAM,依次進行,當寫滿第十個RAM時,將十個RAM緩存的數據寫到對應的FLASH里。FLASH操作按最高速度40MB進行,加載時間為51.2μs,之后進入編程時間,再來的數據繼續緩存在第一個RAM里。相機的時鐘是66 MHz,每個RAM的深度為2048 Bytes,那么寫10個RAM的時間是310μs,即FALSH編程時間可以達到310-51.2=258.8μs,可以滿足FLASH的典型編程時間200μs。其FLASH流水操作見圖4。

5 FLASH壞區管理

對FLASH的壞區實行動態管理,在每個存儲電路板的FPGA內開辟1 K×8 bit的壞區地址存儲。所有存儲電路板的壞區地址一致。在FLASH進行寫操作前比對當前區是否為壞區,如果是壞區則跳過此區進入下一區。

可采用寫入特定數后讀出校驗的方式來檢測壞區。存儲電路板根據命令全區寫入8 bit數據。寫入時序按系統設計的最高速率進行。然后將它們順序讀出并進行校驗,如果出現數據錯誤則登記該壓為壞區。圖5為壞區檢測管理的工作流程。

6 結束語

本文采用多級流水線與并行處理相結合的方式,同時利用FPGA內部的緩存來使多個FLASH存儲器并行工作,從而極大地提高了存儲速率。100片FLASH存儲器同時工作可滿足660 MB/S的速度要求。經過測試,本系統可以可靠地存儲數字圖像,并可屏蔽壞區。

此內容為AET網站原創,未經授權禁止轉載。