當共模信號較難處理或對系統有負面影響的時候,需要進行信號調理。部分系統的設計會將模擬變換器輸出的單端信號轉為全差分信號,然后將這些信號傳送到差分輸入ADC。這種設計的優點是,大部分混入差分線路的噪聲會同時出現在兩條線路上 (假設差分線路都是按差分方式平衡布局)。

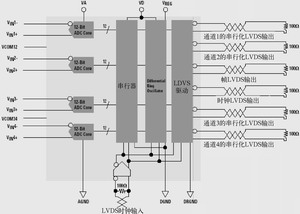

輸入信號轉為數字信號之后,便必須傳送到DSP或ASIC/FPGA,以便進行處理。全差分輸出信號電路通過兩條對稱的線路輸出及吸收電流。低電壓差分信號 (LVDS) 便是這種信號。ADC12QS065 芯片就采用了 LVDS 技術,可解決系統這方面的問題 (見圖 1)。

圖1 ADC12QS065芯片的簡化框圖

電路板布局的比較" border="0" height="172" hspace="0" src="http://files.chinaaet.com/images/20100811/3602e670-eebf-4977-80d9-f17486bd6a2b.jpg" width="300" />

圖2 CMOS 與 LVDS 兩種電路板布局的比較

ADC12QS065內含 4 個 12 位的ADC。芯片的每一個輸入端都可接收全差分信號。此外,這款芯片同時提供的共模輸出參考電壓 VCOM12 及 VCOM34 也可用作輸入共模電壓。ADC12QS065也可選用全差分或單端的時鐘源,只需為 CLK 及 CLKB 提供 LVDS 信號,便可使用 LVDS 時鐘,但要在接近

輸入引腳的位置加設終端電阻。若要利用單端 CMOS 時鐘,便要將 CLKB 置于低電平,這樣便無需加設終端電阻。

每一個ADC將輸出信號串行輸出。輸入時鐘的輸入12倍頻之后,作為 LVDS 時鐘輸出,作為數據采樣時鐘。輸出端也會按照輸入時鐘速率產生 LVDS 幀信號,以便確認取樣數目。

輸出定時將 FPGA 的數據采樣簡化。當取樣數據可送出時,首先輸出幀信號,然后是每個通道的高有效位數據,并輸出一個LVDS時鐘跳變沿信號。LVDS時鐘信號會相對數據輸出偏移1/4周期,以便簡化時鐘管理。每一數據位在時鐘輸出轉換時采樣。采用 LVDS 傳輸技術還有另一優點,即這些信號可以通過符合 EIA/TIA 568 標準的雙絞線傳送。符合這個標準的雙扭線有 100?的特性阻抗。兩根導線距離很近,電流方向相反,只會產生極少的輻射。對于信噪比要求極高的應用來說,這個優點極為重要。

這里利用圖2所示的兩款 4 通道、12 位ADC進一步解釋這一點。左邊的ADC設有傳統的單端并行 CMOS 輸出。若要將轉換器的輸出信號傳送給DSP,便需要 49 條連線 (4 x 12 + 1)。若輸出信號經過串行化處理之后,每一通道僅需要一對差分信號傳輸線。同時也需要輸出時鐘及幀信號。

由于 LVDS 芯片將電源提供的電流從一端送到另一端,因此 LVDS 芯片從電源吸收的電流是連續的,會降低電源的負載變化。這樣做的好處是可以減少供電線路上因負載響應產生的噪聲,減少去耦電容器的體積以及降低布局的要求。

串行 LVDS 芯片可以采用較小的封裝,并更有效地傳送高速信號。但對于許多應用來說,低功耗的特性極為重要。以擁有多條數據通道的系統為例,每一通道所節省的每一 mW 功率加起來便有很大的分別。因此 ADC12QS065除了設有幾個無噪聲驅動器之外,還設有三個獨立的電源輸入。每一個電源輸入都可以連接在一起,成為一個單電源ADC。但這三個電源輸入也可分開,各自獨立操作,為每一電源輸入單獨設計無源濾波器,或干脆使用三個獨立的電源。三個電源各自獨立操作的另一優點是可以將驅動器的輸出電壓降低至 2.5V,這樣有助于降低功耗。

ADC12QS065 也可將其內部電壓參考電路關閉,以便由外部參考源驅動。只要將所有 VREFP 及 VREFN 各自連在一起,便可將多個ADC捆縛一起。這樣做可以確保每一芯片的增益及電壓偏移保持一致,令系統更容易校準。