LEC2 Workbench系列技術(shù)博文主要關(guān)注萊迪思產(chǎn)品的應(yīng)用開發(fā)問題。這些文章由萊迪思教育能力中心(LEC2)的FPGA設(shè)計(jì)專家撰寫。LEC2是專門針對萊迪思屢獲殊榮的低功耗FPGA和解決方案集合的全球官方培訓(xùn)服務(wù)供應(yīng)商。

萊迪思CrossLink?-NX FPGA擁有豐富的特性,可加速實(shí)現(xiàn)高速和低速接口。本文(系列博文的第一篇)描述了使用CrossLink-NX FPGA連接基于SPI的外部組件。第一篇博文介紹了使用兩個(gè)時(shí)鐘域?qū)崿F(xiàn)連接DAC(亞德諾半導(dǎo)體公司的AD7303 DAC)的SPI接口。第二篇博文將介紹使用單個(gè)時(shí)鐘域?qū)崿F(xiàn)連接ADC(亞德諾半導(dǎo)體公司的 ADC AD7476)的SPI接口。兩個(gè)案例中呈現(xiàn)了兩種截然不同的實(shí)現(xiàn)接口的方法。

兩個(gè)時(shí)鐘域的實(shí)現(xiàn)方案(dac_2c)

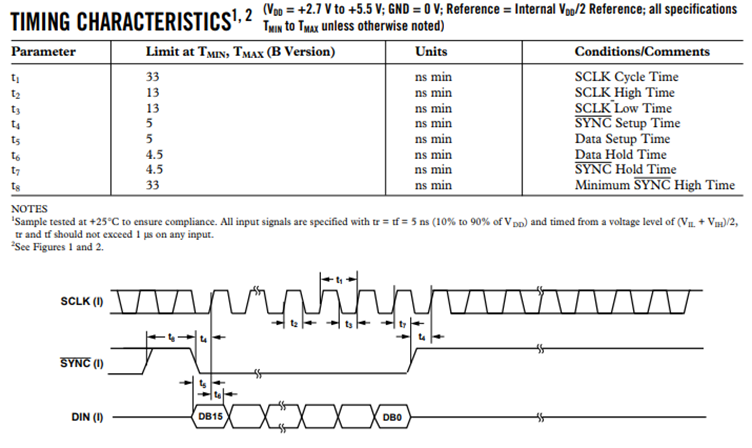

亞德諾半導(dǎo)體公司(ADI)的AD7303模塊用作外部DAC。圖1顯示了接口的時(shí)序圖和時(shí)序參數(shù)。在本例中,SCLK頻率為30 MHz。時(shí)序參數(shù)t4、t5和t6在時(shí)序約束規(guī)范時(shí)尤其需要關(guān)注,它們將在set_output_delay約束中使用。

圖1:時(shí)序圖和時(shí)序特征

兩個(gè)時(shí)鐘域解決方案的實(shí)現(xiàn)如圖2所示。

圖2:兩個(gè)時(shí)鐘域SPI接口的實(shí)現(xiàn)

使用的參數(shù):

輸入時(shí)鐘頻率:100 MHZ

內(nèi)部時(shí)鐘CLK_120頻率:120 MHZ

內(nèi)部時(shí)鐘CLK_30頻率:30 MHZ

生成的時(shí)鐘dac_sck:30 MHZ

PLL_120_30

PLL從外部時(shí)鐘CLK(100 MHz)生成兩個(gè)內(nèi)部相位同步時(shí)鐘CLK_120和CLK_30。

dac_sample_gen模塊

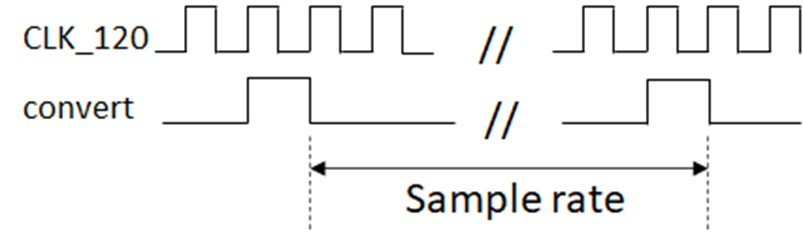

dac_sample_gen模塊為dac_fsm生成采樣信號(轉(zhuǎn)換)。采樣信號開始向DAC傳輸數(shù)字?jǐn)?shù)據(jù)。采樣率通過sample_select [1:0]信號設(shè)置,如表1所示。dac_sample_gen的框圖如圖3所示。

表1:采樣率設(shè)置

圖3:dac_sample_gen的框圖

mode_select控制信號控制方波信號或三角波信號的生成,作為DAC的輸入數(shù)據(jù)。

sync_stage模塊

dac_sample_gen模塊與CLK_120一起工作。控制單元dac_fsm是CLK_30域的一部分。sync_stage模塊將轉(zhuǎn)換信號從CLK_120域傳輸?shù)紺LK_30域。來自dac_fsm的相應(yīng)信號從CLK_30域傳輸?shù)紺LK_120。sync_stage的框圖如圖4所示。

圖4:sync_stage的框圖

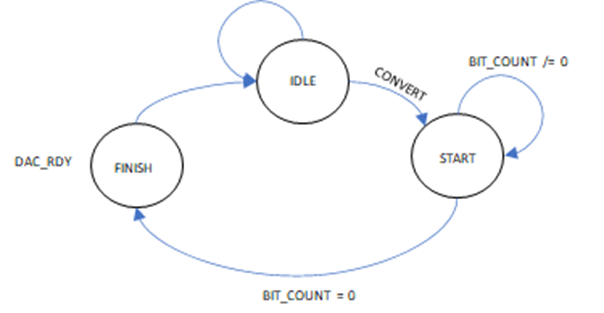

dac_fsm模塊用于雙時(shí)鐘實(shí)現(xiàn)方案

dac_fsm模塊控制生成傳輸?shù)紻AC的控制/數(shù)據(jù)信號。為了遵循圖1給出的t4、t5和t6的值,dac_fsm在CLK_30的下降沿工作。Dac_fsm作為狀態(tài)機(jī)實(shí)現(xiàn)。

圖5:控制結(jié)構(gòu)dac_fsm狀態(tài)機(jī)轉(zhuǎn)換信號被識別后,bit_count計(jì)數(shù)器加載值15。串行數(shù)據(jù)在時(shí)鐘信號CLK_30的下降沿輸出到dac_sdata上。傳輸16位數(shù)據(jù)后,dac_fsm再次發(fā)出就緒信號并等待下一個(gè)轉(zhuǎn)換信號。

約束兩個(gè)時(shí)鐘域解決方案的設(shè)計(jì)

1. 約束時(shí)鐘CLK

2. 約束時(shí)鐘CLK_120和CLK_30

無需明確定義CLK_120和CLK_30這兩個(gè)時(shí)鐘信號,因?yàn)樗鼈儠稍O(shè)計(jì)軟件自動(dòng)定義。這兩個(gè)時(shí)鐘也稱為自動(dòng)生成時(shí)鐘。

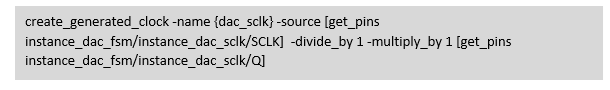

3. 約束dac_clk

連接到端口dac_sck的時(shí)鐘信號是內(nèi)部時(shí)鐘CLK_30的副本。該信號被外部DAC解讀為時(shí)鐘。因此,該信號也必須被定義為時(shí)鐘,便于正確描述t4、t5和t6的時(shí)間要求。該時(shí)鐘即所謂的手動(dòng)生成時(shí)鐘。

4. 約束DAS輸入/FPGA輸出

時(shí)間值t4、t5和t6描述了外部模塊的setup/hold要求。這些要求使用 set_output_delay約束進(jìn)行描述。

運(yùn)行兩個(gè)時(shí)鐘域解決方案的時(shí)序分析

時(shí)序分析報(bào)告顯示了兩個(gè)時(shí)鐘信號CLK_120和CLK_30之間的關(guān)系。

注意CLK_120和CLK_30的跨時(shí)鐘域參數(shù),反之亦然。這正是我們所期望的。

對輸出信號dac_sync和dac_sdata的分析展示了基于set_output_delay約束實(shí)現(xiàn)的setup slack和hold slack。

總結(jié)總之,兩個(gè)時(shí)鐘域提供了一些功耗方面的優(yōu)勢,因?yàn)樵O(shè)計(jì)的一部分以較低的速度運(yùn)行。此外,時(shí)序約束也很容易指定。該項(xiàng)目(dac_2c)可在LEC2索取。欲獲取項(xiàng)目副本,請通過info@lec2-fpga.com與我們聯(lián)系。

我們將在下一篇文章中探討單個(gè)時(shí)鐘域的方法。

Eugen Krassin是萊迪思教育能力中心(LEC2)的總裁兼創(chuàng)始人。