5 月 7 日消息,思科 Cisco 當地時間 6 日宣布推出其量子網絡糾纏芯片原型,同日其量子實驗室也于美國加利福尼亞州圣莫尼卡正式開業。

思科表示,目前的量子處理器所擁有的量子比特規模僅在三位數量級,而最積極的路線圖也僅給出了到 2030 年實現四位數量子比特的展望,這與應用程序所需的數百萬個量子比特間尚有一條鴻溝。

傳統計算此前也曾面臨過類似的問題,最終是通過網絡基礎設施將大量小型節點連接為一個分布式系統的方案取得了成功,而不是一臺足夠大規模的單體計算機。

思科認為量子計算也將遵循這一前例,大批量的量子處理器通過專用量子網絡互聯實現橫向擴展將成為量子計算走向實際應用的必然選擇。

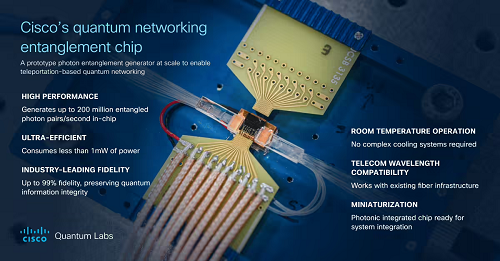

思科的量子網絡糾纏芯片原型由該企業同加州大學圣巴巴拉分校合作開發,通過一對糾纏光子間的量子隱形傳態實現超高速連接。

該芯片利用了硅基 III-V 半導體波導中的自發四波混頻效應,可在室溫下作為小型化 PIC(注:光子集成電路)運行。此外其具備高達 99% 的保真度同時功耗低于 1mW,使用標準 1550nm 電信波長,能與現有光纖基礎設施配合使用。

思科表示這一量子網絡糾纏芯片原型在每個通道上每秒可產生超過 100 萬對可用的糾纏光子,全芯片的糾纏光子產生速率則可達 2 億對。

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:aet@chinaaet.com。