摘 要: 介紹了以MC68HC908JB8為主控芯片的Freescale 16位MCU MC68HC912B32的BDM調(diào)試模式,給出了BDM通信協(xié)議及編程原理、硬件電路圖。

關(guān)鍵詞: BDM MC68HC912B32 BKGD

隨著Flash技術(shù)在微處理器上的廣泛應(yīng)用,使單片機在開發(fā)和應(yīng)用手段上有了革命性的變化,從傳統(tǒng)的仿真器(ICE)到目前流行的JTAG,設(shè)計人員在不斷尋找一種移植性更高、更易操作、費用更低的開發(fā)手段。使用傳統(tǒng)的仿真器進(jìn)行嵌入式開發(fā)時,通常調(diào)試工具會受價格和煩瑣的操作所限制,但是隨著微處理器制造工藝的提高及Flash技術(shù)的發(fā)展,一些高端微處理器(如CPU12/16/32、PowerPC、ColdFire等)內(nèi)部已經(jīng)包含了用于調(diào)試的微代碼,并可以通過背景調(diào)試模式BDM(Background Debug Mode)進(jìn)行調(diào)試。由于這種方法省去了仿真器,因此避免了高頻操作、交直流電不匹配等問題。隨著BDM標(biāo)準(zhǔn)的不斷規(guī)范和普及,用BDM調(diào)試模式進(jìn)行嵌入式開發(fā)已經(jīng)成為一種首選。

MC68HC912B32(以下簡稱B32)是由Freescale公司推出的一款基于CPU12核心的16位嵌入式MCU。它具有體積小、功耗小、功能多等優(yōu)點,主要用于汽車電子、工業(yè)控制、醫(yī)療設(shè)備等領(lǐng)域。它是Freescale公司較早提供的一款背景調(diào)試模式的16位MCU。背景調(diào)試模式是Freescale公司自定義的片上調(diào)試規(guī)范。

1 背景調(diào)試模式介紹

BDM是由Freescale半導(dǎo)體公司推出的一種單線(Single Wire)調(diào)試方式,是目前單片機普遍采用的調(diào)試方式之一。其他公司的嵌入式處理器也有類似的調(diào)試方式,如AMD公司的X86μP系列微處理器提供的AMDebug調(diào)試方式等。

BDM調(diào)試方式為開發(fā)人員提供了底層的調(diào)試手段,開發(fā)人員可以通過它初次向目標(biāo)板下載程序,同時也可以通過BDM調(diào)試器" title="調(diào)試器">調(diào)試器對目標(biāo)板MCU的Flash進(jìn)行寫入、擦除等操作。用戶也可以通過它進(jìn)行應(yīng)用程序的下載和在線更新、在線動態(tài)調(diào)試和編程、讀取CPU各個寄存器的內(nèi)容、單片機內(nèi)部資源的配置與修復(fù)、程序的加密處理等操作。而這些僅需要向CPU發(fā)送幾個簡單的指令就可以實現(xiàn),從而使調(diào)試軟件的編寫變得非常簡單,通常自己就可以編寫。BDM硬件調(diào)試插頭的設(shè)計也非常簡單,關(guān)鍵是要滿足通信時序關(guān)系和電平轉(zhuǎn)換要求。

目前常用的標(biāo)準(zhǔn)BDM調(diào)試插頭如圖1所示,各個引腳信號的定義如表1所示。

?

2 BDM調(diào)試原理

2.1 總體概述

以CPU12為內(nèi)核的MCU的運行模式有單片方式(Single chip)和擴展方式(Expanded Mode)兩種。運行模式主要由BKGD、MODB和MODA引腳的狀態(tài)決定,各個模式與引腳狀態(tài)間的關(guān)系見表2。單片模式又分普通單片模式(Normal Single Chip)和特殊單片模式(Special Single Chip)兩種,而只有在特殊模式下BDM才能被激活,因此特殊單片模式又稱BDM模式。圖2為PC機通過BDM插頭與目標(biāo)機相連。

?

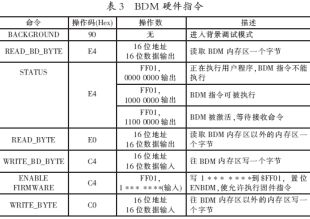

2.2 BDM指令介紹

BDM有兩類指令。一類是在一般運行模式下可以直接執(zhí)行的,被稱為硬件指令(Hardware Command);另一類則是只能在BDM模式下執(zhí)行的程序,這些程序在進(jìn)入BDM模式后被固化在地址為$FF00~$FFFF的ROM中,被稱為固件" title="固件">固件指令(Firmware Command)。

因為BDM控制模塊不在CPU中,所以BDM硬件指令可以在CPU正常運行時被并行執(zhí)行,其他BDM指令是基于固件的,必須在CPU處于BDM模式下才能執(zhí)行。硬件指令允許讀寫目標(biāo)系統(tǒng)內(nèi)(包括片內(nèi)RAM、EEPROM、I/O和控制寄存器等)的所有內(nèi)存。硬件指令可以不在BDM模式下執(zhí)行,表3列出了BDM模塊常用的硬件指令。

固件指令必須在HC12單片機的BDM ROM中執(zhí)行,且CPU必須在BDM模式下才能執(zhí)行,通常使用硬件指令BACKGROUND使CPU進(jìn)入BDM模式。當(dāng)BDM被激活時,BDM ROM就被分配到地址空間:$FF20~$FFFF,同時7個BDM寄存器被分配到地址空間:$FF00~$FF06,此時CPU就可以通過執(zhí)行ROM中的代碼完成相應(yīng)的固件指令操作。表4列出了BDM的7個寄存器,表5介紹了常用的3個固件指令。

2.3 進(jìn)入BDM模式

下面介紹使目標(biāo)機進(jìn)入BDM模式的兩種常用方法。

方法1:將目標(biāo)機的BKGD引腳拉低,然后給目標(biāo)機的RESET引腳加低電平,即給目標(biāo)機復(fù)位,復(fù)位脈沖要足夠?qū)挘辽僖笥谀繕?biāo)機的512個時鐘周期" title="時鐘周期">時鐘周期。本文采用Freescale公司的8位微處理器MC68HC908JB8(簡稱JB8)制作BDM調(diào)試頭,用其PTA0和PTA1口控制目標(biāo)機的RESET和BKGD引腳。此方法通過軟件編程的方式進(jìn)入BDM模式。

方法2:通過硬件跳線的方式將BKGD置低電平,在目標(biāo)機復(fù)位后再將BKGD置高電平" title="高電平">高電平,以進(jìn)入目標(biāo)機的BDM模式。進(jìn)入BDM模式后,帶有BDM程序的片內(nèi)專用ROM將Flash的$FF00~$FFFF替換。此空間在普通單片方式下存放中斷向量。該方法僅通過硬件跳線的方式進(jìn)入BDM模式。

3 B32的BDM調(diào)試系統(tǒng)設(shè)計

3.1 BDM調(diào)試器系統(tǒng)硬件設(shè)計

該BDM調(diào)試器的BKGD和RESET信號分別由JB8單片機的I/O口PTA1、PTA0提供。雙方通信引腳使用漏極開路驅(qū)動(或稱線或)的方式,平時靠上拉電阻維持高電平。Flash編程電源VFP由MAX662提供,MAX662是一款專門提供12V Flash編程電壓的芯片。MAX662外圍電路原理圖如圖3,BDM調(diào)試插頭電路原理圖如圖4。

3.2 BDM調(diào)試器系統(tǒng)軟件設(shè)計

CPU12的BDM通信協(xié)議也稱為單線通信協(xié)議。下面按照該協(xié)議,以JB8作為主控制芯片詳細(xì)介紹B32的BDM調(diào)試系統(tǒng)的軟件設(shè)計。在程序開始前,需要宏定義一些常量以方便下面程序的調(diào)用。具體的宏定義有:

#define DisableInt() asm(″sei″) /*關(guān)閉中斷*/

#define EnableInt() asm(″cli″) /*開放中斷*/

#define PTA *(volatile unsigned char*)0x00

/*A口數(shù)據(jù)寄存器*/

#define DDRA *(volatile unsigned char*)0x04

/*A口方向寄存器*/

3.2.1 調(diào)用讀寫匯編子程序

通過調(diào)用讀寫匯編子程序" title="子程序">子程序,可以讀取和發(fā)送一個字節(jié),具體函數(shù)如下:

INT8U BDMDATA;

void SendOneByte(INT8U c)

{

DisableInt();//關(guān)中斷

BDMDATA=c;//賦值需要發(fā)送的值

_WRITEBYTE();//調(diào)用寫字節(jié)匯編子程序

EnableInt();//開中斷

}

INT8U RecOneByte()

{

DisableInt();//關(guān)中斷

_READBYTE();//調(diào)用讀取字節(jié)匯編子程序

EnableInt();//開中斷

return BDMDATA;//返回讀取的字節(jié)

}

調(diào)用寫子程序的輸入?yún)?shù)是需要被寫的一個字節(jié);調(diào)用讀子程序的返回參數(shù)是讀取到的一個字節(jié)。

3.2.2 讀寫匯編子程序

主機方以下降沿通知目標(biāo)機方的BKGD端,位通信開始,每一位傳輸至少需要16個時鐘周期。具體過程如下:

主機首先拉低BKGD引腳,并使低電平維持時間不短于512個時鐘周期,目標(biāo)機探測到下降沿信號后清命令寄存器,同時等待接收主機的BDM命令。

主機寫位0到目標(biāo)機BKGD端的操作為:主機拉低目標(biāo)機的BKGD端不少于12個時鐘周期,目標(biāo)機在探測到低電平以后的第10個周期對BKGD采樣,讀入該位的0。

主機寫位1到目標(biāo)機BKGD端的操作為:主機拉低目標(biāo)機的BKGD端2~4個時鐘周期后釋放BKGD端,使之為高電平,目標(biāo)機在探測到低電平以后的第10個周期對BKGD采樣,讀入該位的1。

下面是寫一個字節(jié)的匯編代碼:

__WRITEBYTE∷

LDA #$8

_NEXTBIT:

LSL*_BDMDATA //左移待發(fā)送的8位數(shù)據(jù)

BCC_WRITE0 //判斷發(fā)送位

BCLR #1,PTA //PTA.1置低電平

NOP

BSET #1,DDRA //PTA.1定義為輸出

_NEXTBIT1:

BCLR #1,DDRA //PTA.1定義為輸入

NOP

DBNZA _NEXTBIT //判斷字節(jié)是否發(fā)送完畢

_WAIT10:

RTS //返回主程序

_WRITE0: //發(fā)送位“0”

BCLR #1,PTA //PTA1置低電平

NOP

BSET #1,DDRA //PTA1定義為輸出

NOP //空操作,用于控制時序

NOP

NOP

NOP

NOP

NOP

NOP

BRA_NEXTBIT1 //發(fā)送下一位

主機讀目標(biāo)機BKGD端的信息時,主機拉低目標(biāo)機BKGD端2~4個周期后釋放BKGD端,然后定義該引腳為輸入狀態(tài),讀取BKGD端的電平。如果目標(biāo)機輸出為0電平,則繼續(xù)拉低BKGD端,從探測到主機拉低BKGD端起持續(xù)13個時鐘周期。所以主機的讀操作應(yīng)在從拉低BKGD線算起的13個時鐘周期內(nèi)完成。對于目標(biāo)機輸出為1的情況,無需目標(biāo)機輸出高電平,因為BKGD端已用電阻上拉,只需定義該引腳為輸入,則自然會使之為1。

下面是讀取一個字節(jié)的匯編代碼:

__READBYTE∷

LDA #8

_NEXTBITR:

PSHA //A進(jìn)棧

LDA #01

BCLR #1,PTA //PTA.1置低電平

BSET #1,DDRA //PTA.1定義為輸出

BCLR #1,DDRA //PTA.1定義為輸入

NOP

LDA PTA //讀取BKGD引腳狀態(tài)

NOP

NOP

NOP

LSRA //將讀取位移入標(biāo)志位C

LSRA

ROL *BDMDATA //將讀取的位存入變量

PULA

DECA

BNE _NEXTBITR //判斷字節(jié)是否讀取完畢

RTS //返回主程序

對于硬件命令,命令之間間隔要大于150個時鐘周期;對于固件命令,送出讀命令到讀取數(shù)據(jù)之間要延遲32個時鐘周期;寫命令后面可緊跟需要寫的數(shù)據(jù),但與下一條命令之間要間隔32個時鐘周期。

3.2.3 測試程序

為了測試以上程序的正確性,特用VC6.0編寫了一個計算機端的測試程序。該程序通過串口與JB8通信,以完成對B32 Flash的讀寫和擦除。由于源代碼較長,限于篇幅不在此列出。

參考文獻(xiàn)

1 Freescale.M68HC12B Family Data sheet.Rev.9,2004

2 Freescale.CPU12 Reference Manual.Rev.3,2002

3 Freescale.A Serial Bootloader for Reprogramming the MC68HC912B32 Flash.E2PROM,1997

4 Freescale.MC68HC90908JB8/D.Rev.1.0,2000