為了削減成本,提升性能和保持靈活性,在工業(yè)、醫(yī)療、汽車、航天和軍用產(chǎn)品等廣泛的應用領域,包括處理器和外設在內(nèi)的完整的嵌入式系統(tǒng)被整合到了FPGA 上。

雖然FPGA的傳統(tǒng)用戶是硬件設計者,但是賽靈思的新型嵌入式設計平臺,使得軟件開發(fā)人員也能夠在熟悉的環(huán)境中輕松編程,包括Eclipse IDE、編譯器、調(diào)試器、操作系統(tǒng)和庫。編程可以利用uC/OS-II之類的RTOS 甚至全嵌入式Linux在裸金屬級完成。

圖1 嵌入式目標參考設計

嵌入式設計趨勢及挑戰(zhàn)

FPGA的應用到現(xiàn)在已經(jīng)有二十多年的時間了,我們在各個領域都能看到各種FPGA的應用,例如醫(yī)療、工業(yè)控制、汽車電子、連接IP、高端顯示、無線、監(jiān)控、軍事通信等等。然而,F(xiàn)PGA內(nèi)使用嵌入式處理器的時間只不過是近十年的事情,從1999年到現(xiàn)在,F(xiàn)PGA內(nèi)使用嵌入式處理器在逐年正向增加中。

圖2 EDK 軟件、硬件和集成流程

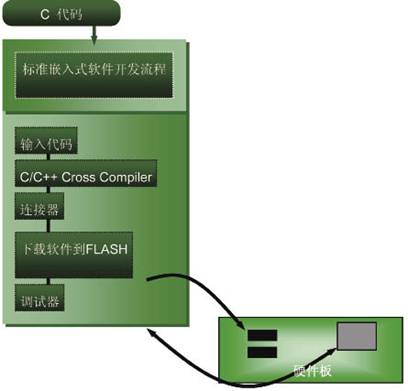

圖3 簡單的SDK軟件開發(fā)流程步驟

隨著FPGA內(nèi)使用嵌入式處理器設計越來越多,我們面臨的挑戰(zhàn)也越來越多,主要挑戰(zhàn)分為三個方向:

• 滿足不斷提高的技術要求

–要求有一個適用于該應用的處理器系統(tǒng)

–要求能夠選擇正確的功能(外設)組合

• 即便只有很少的FPGA設計經(jīng)驗,也能開發(fā)軟件

–需要易于定制的預配置系統(tǒng)

• 降低進度風險

–希望花更少的時間創(chuàng)建和調(diào)試定制IP模塊

–快速并行開發(fā)和驗證軟硬件

很多人都使用過嵌入式處理器,但當一開始在選擇一個嵌入式處理器作為系統(tǒng)核心時,考慮要點是什么呢?一個適用于該系統(tǒng)應用的處理器以及能夠正確滿足外設功能需求的組合將會是最后的選擇。這些選擇處理器的條件都是FPGA嵌入式處理的挑戰(zhàn)。

除此之外,F(xiàn)PGA硬件設計的難度必須要有效降低,能讓對FPGA經(jīng)驗設計較少的人員也能夠開發(fā)軟件,這點是因為傳統(tǒng)的FPGA設計工程師,他們雖然沒有硬件的設計經(jīng)驗也要能夠開發(fā)軟件,這就必須要有一個易于制定的預配置系統(tǒng)。

在進度風險的管理上,F(xiàn)PGA嵌入式設計顯得額外重要,由于FPGA嵌入式設計包含軟件和硬件同時在一個芯片上,所以當問題發(fā)生時,硬件人員和軟件人員并不能很快理清問題的癥結(jié)點,所以常常延遲進度,因此在選擇FPGA嵌入式系統(tǒng)時,使用人員往往希望花更少的時間來調(diào)試硬件IP模塊,并同時開發(fā)驗證軟件,軟硬件的整合和效能提升是一個很大挑戰(zhàn)。

賽靈思嵌入式平臺

賽靈思基于FPGA的嵌入式平臺的基本價值在于為了滿足不斷提高的客戶要求。而嵌入式目標參考設計可以讓對FPGA設計經(jīng)驗很少的人也能夠快速開發(fā)軟件。而內(nèi)含目標參考設計Spartan-6和Virtex-6的嵌入式套件可以有效地管理降低客戶開發(fā)進度風險。

Spartan-6 FPGA嵌入式套件

• 描述:

–該套件支持使用MicroBlaze軟處理器的軟件開發(fā)工作以及使用Spartan-6 LX45T FPGA的硬件處理器系統(tǒng)定制工作。

• 組件:

–采用Spartan-6 LX45T FPGA的SP605基礎板

• 下載/調(diào)試電纜、電源

–ISE設計套件:嵌入式版本

• ISE和 ChipScope Pro:S6LX45T專用的器件

• Platform Studio、軟件開發(fā)套件(SDK) (Eclipse IDE)

–嵌入式目標參考設計

• MicroBlaze™處理器子系統(tǒng)設計

–技術文檔

• 硬件設置指南和入門指南

• 深入的硬件和軟件分步輔導資料

–生態(tài)系統(tǒng)合作伙伴提供OS/RTOS支持

• Linux、uC/OS-II、TreckVirtex-6 FPGA嵌入式套件

• 描述:

–該套件支持使用MicroBlaze軟處理器的軟件開發(fā)工作以及使用Virtex™-6 LX240T FPGA的硬件處理器系統(tǒng)定制工作

• 組件:

–采用Virtex-6 LX240T FPGA的 ML605基礎板

• 下載/調(diào)試電纜、電源

–ISE設計套件:嵌入式版本

• ISE和ChipScope Pro:V6LX240T專用的器件

• Platform Studio、軟件開發(fā)套件(SDK) (Eclipse IDE)

–嵌入式目標參考設計

• MicroBlaze處理器子系統(tǒng)設計

–技術文檔

• 硬件設置指南和入門指南

• 深入的硬件和軟件分步輔導資料

–生態(tài)系統(tǒng)合作伙伴提供OS/RTOS 支持

• Linux、uC/OS-II、Treck

圖4 簡單硬件設計流程步驟

圖5 集成并優(yōu)化軟件/硬件

嵌入式目標參考設計

Spartan-6和Virtex-6嵌入式目標參考設計其實是非常相象的,它們都包含一個32位的MicroBlaze™RISC處理器,性能優(yōu)化,支持Linux RTOS,100MHz時鐘頻率。另外還包含集成式存儲控制器,包含DDR、DDR2、DDR3、LPDDR,數(shù)據(jù)速率達800Mbps。

全套優(yōu)化的軟IP外設和總線結(jié)構包含UART、Flash、GPIO、I2C/SPI、Timer/Intr Controller、Debug。具體如圖1所示,參考設計中集成以太網(wǎng)MAC IP,資源百兆、千兆網(wǎng),子IP也可與外部碼作整合。處理器和處理器子系統(tǒng)全面可操作且簡便易用,有助于立即著手系統(tǒng)開發(fā)工作。

MicroBlaze處理器子系統(tǒng)

Spartan-6和Virtex-6嵌入式參考設計中,提供MicroBlaze處理器子系統(tǒng),稱為PSS(processer sub system),通過這樣一個PSS子系統(tǒng),用戶可以很快地將自己的定義邏輯加入這樣一個子系統(tǒng)中,由于這個目標參考設計MicroBlaze子系統(tǒng)已經(jīng)整合了許多外設功能,用戶制定的這個邏輯便可以很快地通過網(wǎng)絡來控制或者讓DDR內(nèi)存作存儲,這將有效降低客戶在開發(fā)過程中的時間。

操作步驟

提高效率只需簡單幾步,第一步,數(shù)分鐘內(nèi)啟動設計,包括連接電纜,接通開發(fā)板電源,載入嵌入式平臺演示;第二步,評估,包括評估嵌入式平臺演示,用互動界面評估性能參數(shù);第三步,定制,包括啟動嵌入式目標參考設計項目,根據(jù)軟件開發(fā)輔導資料對軟件應用進行編程、調(diào)試和描述,根據(jù)硬件開發(fā)輔導資料進行設計修改。

在經(jīng)過第一步和第二步之后,用戶已經(jīng)充分了解嵌入式目標參考設計的內(nèi)容,并可利用嵌入式目標參考設計來加入用戶自己的邏輯和自己的軟件,使用XPS進行硬件制定的開發(fā),使用SDK進行軟件的開發(fā),這樣就可以按時完成設計要求。

EDK是Xilinx嵌入式開發(fā)套件,其主要工具XPS是集成標準硬件流程ISE以及標準軟件流程SDK。XPS本身并不實現(xiàn)硬件流程,是通過呼叫ISE來達成硬件流程的實現(xiàn)。硬件流程包含了標準的FPGA硬件發(fā)展流程。XPS也不實現(xiàn)標準軟件流程,也是通過呼叫SDK來實現(xiàn)標準軟件流程。用戶可以通過XPS對系統(tǒng)作描述,如圖2所示。可以稱XPS為一個腳本產(chǎn)生器,是用來聯(lián)絡硬件和軟件流程的工具。

簡單的SDK軟件開發(fā)流程步驟如圖3所示,這些都將在SDK上完成。

• 采用SDK Eclipse IDE開始設計

• 打開專門針對MicroBlaze PSS 目標參考設計配置的工作區(qū)(Workspace)

• 編程

• 創(chuàng)建獨立的軟件平臺或OS BSP

• 創(chuàng)建、編譯并構建軟件應用

• 用圖形調(diào)試器調(diào)試軟件應用

簡單硬件設計流程步驟如圖4所示。

• 用XPS開始設計

• 啟動MicroBlaze PSS目標參考設計項目

• 修改

• 從EDK套件中選擇其他標準外設添加到PSS

• 根據(jù)“創(chuàng)建IP向?qū)?rdquo;創(chuàng)建定制IP

• 根據(jù)“調(diào)試配置向?qū)?rdquo;添加ChipScope調(diào)試IP

集成并優(yōu)化軟件/硬件的步驟如圖5所示。

• 用 ChipScope™Pro 分析工具調(diào)試軟件/硬件集成問題

• 用SDK描述應用并確定熱點

• 下載性能關鍵代碼(performance critical code)到硬件加速器

第三方提供嵌入式軟件支持主流的有Linux (PetaLinux)、uC/OS-II和Treck 網(wǎng)絡中間件,主要特性如表1所示。

表1 生態(tài)系統(tǒng)合作伙伴主要特性

總結(jié)

最后總結(jié)一下,新型嵌入式開發(fā)套件可最大限度地縮短開發(fā)時間也就是加速產(chǎn)品上市進程,采用預集成組件降低風險,也就是新型目標參考設計可幫助設計人員提高工作效率。可以使設計人員致力于實現(xiàn)產(chǎn)品差異化和增值。