0 引言

RapidIO互連構(gòu)架作為一種基于可靠性的開放式互連協(xié)議標(biāo)準(zhǔn),以其高效率、高穩(wěn)定性、低系統(tǒng)成本等特點(diǎn),可為通信系統(tǒng)各器件間提供高帶寬、低延時(shí)數(shù)據(jù)傳輸?shù)慕鉀Q方案。同時(shí),它還擁有支持點(diǎn)對(duì)點(diǎn)或點(diǎn)對(duì)多點(diǎn)的通信能力,并支持DMA操作和消息傳遞,同時(shí)支持多種拓?fù)浣Y(jié)構(gòu),因而可為數(shù)據(jù)處理性能的穩(wěn)定快速提升提供強(qiáng)有力的保障。Tundra公司的TSI578是第三代交換機(jī)芯片,可支援串列RapidIO的處理器與周邊設(shè)備的互連。該交換芯片可支持80Gb/s的聚合帶寬。借助TSI578系列交換機(jī),用戶可用較低的成本開發(fā)出功能強(qiáng)大、性能卓越的系統(tǒng)。T-SI578可為設(shè)計(jì)人員和架構(gòu)工程師提供極強(qiáng)的伸縮性。

如何設(shè)計(jì)基于RapidIO接口的高速電路的信號(hào)完整性性能是關(guān)鍵問題,因此,本文在介紹TSI578硬件設(shè)計(jì)的基礎(chǔ)上,也簡(jiǎn)要說明了高速電路板的設(shè)計(jì)方法,并給出了SRIO信號(hào)的眼圖。

1 硬件設(shè)計(jì)方案

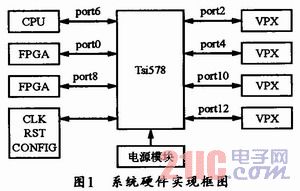

本系統(tǒng)的硬件實(shí)現(xiàn)框圖如圖1所示。該平臺(tái)以TSI578芯片為核心,同時(shí)集成了2片F(xiàn)PGA和一片CPU。其中TSI578可提供8個(gè)4X模式的SRIO端口,CPU和2個(gè)FPGA分別連接到TSI578的其中一個(gè)4X端口上,并通過SRIO實(shí)現(xiàn)互連,以對(duì)外提供4個(gè)4X SRIO接口用于與背板之間的數(shù)據(jù)交換。由于TSI578的應(yīng)用設(shè)計(jì)方法是本文側(cè)重介紹的內(nèi)容,因此,下面主要介紹該交換芯片的硬件應(yīng)用設(shè)計(jì)方案。

1.1 SRIO交換器件

TSI578交換機(jī)芯片具有非常高的應(yīng)用伸縮性,可廣泛應(yīng)用于聯(lián)網(wǎng)、無線與視頻基礎(chǔ)架構(gòu)等領(lǐng)域,因此,設(shè)計(jì)者可以充分利用配置選件來有效地管理電源需求,從而進(jìn)一步提高性能。TSI578可靈活地支援多達(dá)8個(gè)4x mode或16個(gè)1xmode的埠,每個(gè)埠可配置為1.25Gb/s、2.5Gb /s或3.125 Gb/s。而且交換機(jī)的所有埠完全獨(dú)立,可支援各種寬度與速度配置。

TSI578具有以下特點(diǎn):

◇伸縮性極強(qiáng),靈活的埠可支援各種埠寬度與速度,并可提供適用于網(wǎng)狀、光纖與集成系統(tǒng)的單一解決方案;

◇有群播功能,可改善分散式處理性能;

◇有通信流監(jiān)控功能,可提高性能與光纖管理功能;

◇增強(qiáng)的SerDes可最大限度地降低功耗。

1.2 TSI578供電設(shè)計(jì)

TSI578芯片需要3種電源,其中內(nèi)核供電電壓為1.2 V,I/O供電電壓為數(shù)字3.3 V,SERDES供電電壓為模擬3.3 V。由于本模塊沒有對(duì)噪聲比較敏感的音頻和射頻等模擬電路,故可以采用DC-DC電路來減少功耗。設(shè)計(jì)時(shí)可選取凌特IXM4600模塊來分別產(chǎn)生3.3 V和1.2 V。該模塊具有高轉(zhuǎn)換效率、簡(jiǎn)單的外圍電路、更小的封裝、低紋波電壓等特點(diǎn)。需要說明的是:TSI578芯片對(duì)于上電、斷電時(shí)序有著嚴(yán)格的要求,上電的順序依次為1.2 V、數(shù)字3.3 V、模擬3.3 V,斷電的順序依次為模擬3.3 V、數(shù)字3.3 V、1.2 V。本設(shè)計(jì)采用Intersil公司的ISL6123來控制TSI578芯片的上電時(shí)序,ISL6123芯片通過在相應(yīng)的引腳連接不同容值的電容可控制輸出加電控制信號(hào)的時(shí)間。

1.3 時(shí)鐘設(shè)計(jì)

TSI578芯片需要3個(gè)時(shí)鐘源,其中一路156.25MHz差分對(duì)時(shí)鐘輸入(S_CLK_p/n)用來控制信號(hào)的傳輸速率,另一路100 MHz共模時(shí)鐘信號(hào)(P_CLK)用以控制TSI578內(nèi)部寄存器的訪問。另外,由100 MHz的高穩(wěn)晶振產(chǎn)生的時(shí)鐘信號(hào)經(jīng)過驅(qū)動(dòng)芯片后,其中一路可提供P_CLK時(shí)鐘,另外一路經(jīng)過AD9516芯片產(chǎn)生所需的差分時(shí)鐘信號(hào)S_CLK_p/n。RapidIO數(shù)據(jù)的傳輸波特率可通過管腳,分別設(shè)置為1.25G、2.5G和3.125G。

1.4 復(fù)位設(shè)計(jì)

外部復(fù)位信號(hào)在輸入后,可與手動(dòng)復(fù)位信號(hào)一起作為邏輯門的輸入,邏輯門的輸出連接至FPGA的復(fù)位控制管腳,從FPGA產(chǎn)生的復(fù)位信號(hào)可直接提供給TSI578以及其它芯片作為復(fù)位輸入。

2 基于信號(hào)完整性的高速電路板設(shè)計(jì)

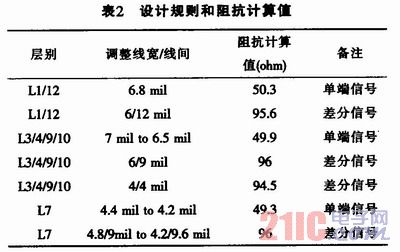

對(duì)于高速電路板來說,信號(hào)完整性問題是非常關(guān)鍵的一個(gè)問題。信號(hào)完整性設(shè)計(jì)包括兩個(gè)方面,一個(gè)是原理圖中的信號(hào)完整性設(shè)計(jì),另一個(gè)是PCB中的信號(hào)完整性設(shè)計(jì)。在原理圖設(shè)計(jì)中,主要考慮反射和地彈效應(yīng)。對(duì)于以上兩個(gè)效應(yīng)的處理,可分別采用阻抗匹配和去耦電容兩種方法進(jìn)行處理。為了更好的解決信號(hào)完整性問題,通常只局限于原理圖設(shè)計(jì)是遠(yuǎn)遠(yuǎn)不夠的,更多的工作還在PCB的設(shè)計(jì)中。PCB中的信號(hào)完整性分析包括布線前仿真和布線后仿真,前仿真是指在PCB布局、布線之前,對(duì)原理圖中的高速信號(hào)進(jìn)行仿真,以考察信號(hào)在虛擬的疊層結(jié)構(gòu)與布線參數(shù)下的傳輸效果,幫助設(shè)計(jì)者優(yōu)化出一套適合當(dāng)前電路的PCB疊層結(jié)構(gòu)、布線阻抗與高速設(shè)計(jì)規(guī)則(線寬、線長(zhǎng)、間距等)。后仿真則提供批處理仿真功能,它對(duì)PCB進(jìn)行整板或關(guān)鍵網(wǎng)絡(luò)進(jìn)行交互式仿真分析,輸出精確的信號(hào)波形、電磁輻射頻譜或眼圖,設(shè)計(jì)者可以修改布線參數(shù)后再仿真,從而發(fā)現(xiàn)并改善不合理的布線。本設(shè)計(jì)中的SRIO信號(hào)是關(guān)鍵的高速信號(hào),根據(jù)PCB仿真結(jié)果設(shè)計(jì)出的PCB疊層結(jié)構(gòu)和設(shè)計(jì)規(guī)則如表1和表2所列。

3 試驗(yàn)結(jié)果

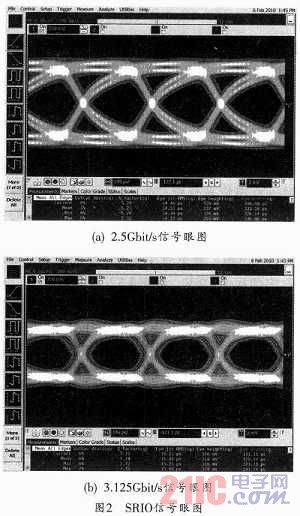

依據(jù)本方案設(shè)計(jì)的交換模塊經(jīng)長(zhǎng)期試驗(yàn),運(yùn)行穩(wěn)定,數(shù)據(jù)傳輸帶寬高。圖2所示是示波器測(cè)量的信號(hào)工作于2.5Gb/s(見圖2(a))和3.125Gb/s(見圖2(b))時(shí)的眼圖。從圖2可看出,該接口即使在3.125Gb/s模式下工作,仍然能夠保持很好的信號(hào)完整性,可以滿足SRIO信號(hào)的判決條件。

4 結(jié)束語(yǔ)

本文介紹了基于TSI578芯片的RapidIO交換模塊的設(shè)計(jì)原理和實(shí)現(xiàn)方法,并在電路設(shè)計(jì)中運(yùn)用仿真技術(shù)確保了高速電路設(shè)計(jì)的正確性。隨著科學(xué)技術(shù)的發(fā)展,基于RapidIO接口的模塊會(huì)被越來越多的使用,交換模塊將成為RapidIO互連構(gòu)架中交換模塊系統(tǒng)設(shè)計(jì)的一種重要組件模塊,并在嵌入式系統(tǒng)中得到廣泛的應(yīng)用。