1 引言

VME 總線由于具有良好的物理特性、嚴(yán)格的技術(shù)規(guī)范和與微處理器接口靈活的特點而 被廣泛應(yīng)用于雷達、聲納等大規(guī)模并行多處理器系統(tǒng)[1],在國內(nèi)外船舶機艙自動化控制系統(tǒng) 中也有成功應(yīng)用。用戶在開發(fā)基于VME 總線的信號采集模塊時,首先必須考慮和解決的是 與VME 總線的接口問題。本文采用基于GAL 芯片實現(xiàn)VME 總線接口電路的思路,對VME 總線接口設(shè)計問題進行了深入研究。文中通過軟件技術(shù)實現(xiàn)了VME 總線地址的譯碼以及數(shù) 據(jù)讀寫與中斷邏輯控制,有效簡化了硬件電路的設(shè)計。

2 接口設(shè)計功能要求

根據(jù) VME 總線規(guī)范和本題具體任務(wù)需求,本文設(shè)計的VME 總線接口電路為一從控設(shè) 備接口電路(Slave Interface),接口的數(shù)據(jù)總線寬度和地址總線寬度均為16 位。主要接口功 能要求如下:

1)產(chǎn)生電路板本身的程序復(fù)位和硬件復(fù)位信號;

2)產(chǎn)生I/O 讀、寫信號及數(shù)據(jù)總線接口芯片片選信號;

3)產(chǎn)生與VME 總線的應(yīng)答信號、數(shù)據(jù)選通信號,控制數(shù)據(jù)傳送方向;

4)具有中斷請求功能:可設(shè)定的中斷請求級;可編程中斷向量;支持中斷響應(yīng)菊花鏈。

3 主要接口電路設(shè)計與功能實現(xiàn)

3.1 接口設(shè)計原理

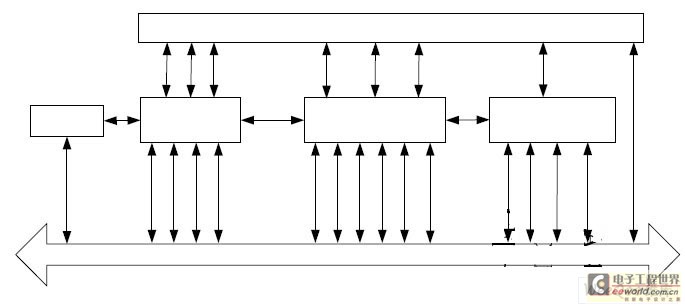

通過比較研究,本文選用 Lattice 的通用陣列邏輯(GAL)芯片來完成接口邏輯電路設(shè) 計。GAL 芯片是Lattice 公司開發(fā)的電可擦寫、可重復(fù)編程的PLD,具有結(jié)構(gòu)簡單,易于編 程等優(yōu)點。本文采用3 片GAL 芯片進行接口邏輯電路設(shè)計,電路基本結(jié)構(gòu)及原理如圖1 所 示。圖中2 片GAL20V8 完成地址譯碼和讀寫控制,1 片GAL16V8 完成中斷請求控制,數(shù) 據(jù)接口采用通用總線接口芯片Z8536。Z8536 是一種帶有兩個8 位I/O 口、通用可編程的總 線接口芯片。通過對控制寄存器進行配置,可將這兩個I/O 口作為兩路8 位信號通道,或共 同構(gòu)成一路16 位信號的通道。在本設(shè)計中,GAL 芯片將VME 總線*問Z8536 的信號進 行譯碼,再通過LA4 和LA5 對Z8536 各個接口及工作方式配置寄存器進行選擇。VME 總 線借助Z8536 即實現(xiàn)對該從板上8 位或16 位數(shù)據(jù)的讀寫。

圖1 電路基本結(jié)構(gòu)及原理

3.2 地址譯碼和讀寫控制電路設(shè)計與功能實現(xiàn)

地址譯碼電路要實現(xiàn)的主要功能是當(dāng)主設(shè)備發(fā)出的地址有效信號AS*有效時,自動從 總線上獲取地址和地址修飾碼,然后根據(jù)地址修飾碼配置本次地址傳送的方式,再根據(jù)地址 發(fā)出相應(yīng)的片選信號選擇板上芯片。讀寫控制模塊的主要功能是通過讀寫周期時序內(nèi)產(chǎn)生的 DS0*、DS1*、WRITE*、LWORD*、IACK*等信號正確配置數(shù)據(jù)傳送的形式,控制板上的 I/O 芯片的讀寫,并發(fā)出DTACK*信號還原主設(shè)備[2]。

為滿足以上要求,地址譯碼芯片上的CE[3~0]分別接4 片Z8536 總線接口芯片的使能端; 讀寫控制芯片上的RD 和WR 分別接Z8536 的讀寫使能端。通過這兩塊芯片,實現(xiàn)了VME 總線對該從板上各路信號的讀寫進行的控制。

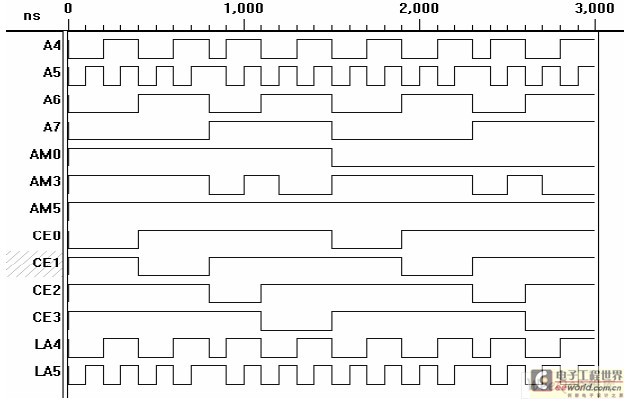

由以上分析及邏輯推理確定了 GAL 芯片要實現(xiàn)的功能以后,根據(jù)總線協(xié)議和硬件電路 即可得到相關(guān)信號之間的邏輯關(guān)系,本文據(jù)此完成了相應(yīng)ABEL-HDL 程序編寫并利用 Lattice 公司的專用開發(fā)工具ispLEVER5.1 對GAL 芯片程序進行了編譯和仿真調(diào)試,其地址 譯碼控制過程仿真波形如圖2 所示。

圖 2 地址譯碼控制過程仿真波形

3.3 中段請求控制電路設(shè)計與功能實現(xiàn)

VME 優(yōu)先級中斷機制采用菊花鏈,它用于在板與板之間傳送一電平信號。它始于第一 槽而終結(jié)于最后一槽。系統(tǒng)可以提供IRQ 1 ~IRQ7 共7 個中斷請求,其中IRQ7 具有最高優(yōu) 先級。本文采用通過跳線設(shè)定優(yōu)先級的方法。當(dāng)中斷處理器處理中斷請求時,中斷應(yīng)答菊花 鏈驅(qū)動器啟動中斷應(yīng)答菊花鏈工作,以確保只有一個中斷器響應(yīng)正在進行中的中斷應(yīng)答周 期。當(dāng)主設(shè)備應(yīng)答某個中斷時,首先把IACK*信號驅(qū)動為低,表示當(dāng)前周期是中斷應(yīng)答周 期,同時將相應(yīng)的中斷請求級別值放到A01~A03 上。而中斷響應(yīng)主要由中斷響應(yīng)輸入 (IACKIN*)和中斷響應(yīng)輸出((IACKOUT*)組成應(yīng)答菊花鏈。若某一從設(shè)備發(fā)出中斷請求,并 且響應(yīng)的中斷識別碼和自己匹配,同時接到上一級傳下來的有效的IACKIN*信號,則判斷 是自己的中斷響應(yīng),應(yīng)該堵塞IACKOUT*信號,使之為高電平,否則應(yīng)該繼續(xù)下傳 IACKOUT*信號[3]。根據(jù)上述的VME 總線中斷處理機制和過程,可以設(shè)計出在Slave 模式 下,從設(shè)備通過GAL 芯片申請中斷的控制邏輯。中斷控制邏輯部分的ABEL-HDL 源程序 如下:

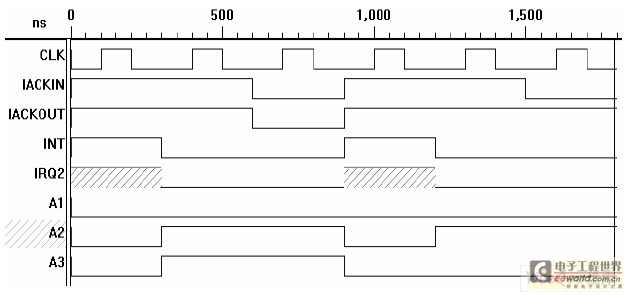

圖 3 是該程序在ispLEVER5.1 中的仿真波形圖。在該圖中,從設(shè)備板上的Z8536 通過 將INT 拉低請求一個權(quán)限為IRQ2 的中斷,譯碼識別代碼為010。由圖可見,當(dāng)A[3~1]為 010 時,菊花鏈停止傳送,否則由IACKOUT 傳出。

圖 3 中斷請求控制仿真波形

4 結(jié)語

目前基于上述接口電路的VME 總線I/O 接口板卡設(shè)計研制工作已完成,并已成功應(yīng)用 于機艙自動化控制系統(tǒng)原理樣機中。試運行以來穩(wěn)定可靠,表明本文設(shè)計思路方法可行,電 路及程序?qū)崿F(xiàn)達到預(yù)期目標(biāo),為VME 總線接口邏輯功能的設(shè)計與實現(xiàn)提供了一條途徑。

本文創(chuàng)新點:VME 總線接口電路設(shè)計方法有多種,本文利用可編程邏輯器件,通過軟 件手段實現(xiàn)VME 總線地址譯碼以及數(shù)據(jù)讀寫與中斷控制邏輯,使總線接口電路得到了有效 的簡化。