隨著FPGA性能和容量的改進,使用FPGA執行DSP功能的做法變得越來越普遍。在許多情況下,同一應用中同時使用處理器和FPGA,采用協處理架構,讓FPGA執行預處理或后處理操作,以加快處理速度。本文說明如何將FPGA和與固定功能DSP結合起來使用,設計一個基于多普勒測量原理的非侵入式測量系統。

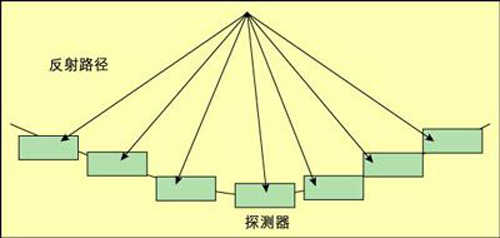

圖1:電子束聚集技術。

傳統上,大量的應用設計使用專門的數字信號處理(DSP)芯片或專用標準產品(ASSP)并通過信號處理算法來處理數字信息,濾波、視頻處理、編碼與解碼、以及音頻處理等僅僅是眾多采用 DSP 的應用中的一部分而已。

現在,隨著 FPGA 性能和容量的改進,以及可以在大多數 DSP 應用中看到的通用算術運算的效率的提高,使用FPGA執行DSP功能的做法變得越來越普遍。在許多情況下,同一應用中同時使用處理器和FPGA,采用協處理架構,讓FPGA執行預處理或后處理操作,以加快處理速度。

顯示此種趨勢的應用之一是多普勒測量系統,它可以測量固體或液體在各種環境中流動的速度。從管道中流動的油,到人的心臟中流動的血液,相對于以前的方法,基于多普勒測量原理的非侵入式測量方法可以極大地降低風險,減少成本和提高精度。一般來說,這些系統都是采用 DSP技術,將FPGA和如TI公司提供的固定功能DSP器件之類結合起來使用。

多普勒測量系統

多普勒測量系統利用多普勒效應測量運動目標(固體、液體或氣體)的速度。最著名的應用大概要算雷達槍了,交通巡警利用它檢測超速汽車。

在測量除汽車速度之外的其他物體的運動(例如心臟中血液的流動)時,需要進行多種測量,來確定更為復雜的流動的細節。方法之一是利用電子束聚集技術。

在這種技術中,將使用大量探測器(許多小雷達槍)測量從發射源返回的頻率。這些探測器沿拋物線分布(如圖1 所示),因此從焦點返回的信號將會同時到達每個探測器。將這些信號組合起來,并對顯著速度的微小波動進行少量處理,就可以確定位于焦點處的物體的速度。如果可以移動探測器來對整個關注區域進行掃描,那么這種方法效果會相當好,但是如果沒有這樣的條件,則可以采用另外一種技術,它可以獲得同樣的結果。通過插入一定的可編程的延遲,改變各個探測器的輸入組合的時間,可以將焦點改變到關注區域中的幾乎任何位置。例如,加入一定的固定額外延遲可以使焦點遠移,而改變延遲來縮短探測器一側的傳播路徑則會使焦點向該側移動。

圖2 顯示了如何利用可調延遲產生拋物線形效果。可調延遲功能在富含寄存器的FPGA中極易實現,并可能成為從傳統DSP中剝離作為協處理器功能的一種功能。

系統實現示例

圖 3 顯示了一種系統實現示例的框圖。位于圖中部的 FPGA 負責產生發射器使用的輸出信號。該實現采用

圖2:具有延遲功能的電子束聚集技術。

探測器測量返回信號的模擬值,產生饋送到FPGA的數字值。FPGA對輸入信號執行部分初步濾波運算,來調整探測器的位置。然后FPGA向每個探測器數據流中插入一定可編程延遲,以實現電子束聚集功能。數據流被組合起來,一個數字濾波器負責確定信號的頻率分量。這樣就得到了確定焦點速度所必需的多普勒讀數。

在FPGA的內部有一個MicroBlaze軟核,控制著測量過程,從而實現高層次的功能,如掃描、初始化、測試,以及診斷等。

DSP讀取和存儲FPGA執行操作的結果。一旦完成一系列掃描,處理器就可以構建出一幅針對掃描區域的數字圖像。可以為不同的速度分配不同的顏色(按照線性、對數或任何其他比例),并將數字圖像轉換成視頻圖像,在圖形終端上實時顯示或記錄下來留待以后回放。利用眾多可以得到的軟件或工具包中的一個,還可以在處理器中輕松實現到JPEG或其他視頻格式的轉換, 還可以采用其他系統分割進行實驗。如果實時視頻處理和存儲占用了處理器過多帶寬,可以將算法的一部分(比如掃描數據的預處理)放在FPGA中來執行。

測量過程的另一個重要部分是確定目標的質量。可以通過測量從焦點返回探測器的能量大小來實現這一功能。返回的能量越多,則目標越大(一般而言)。當測量的目標具有固定連貫性時(如在管道中流動的油或其他液體),這種測量效果特別好,但當系統中存在各種不同質量或反射時,測量就很困難了。

顯然,對被測系統多些了解可以為測量過程提供一些線索。通過存儲與返回信號的幅度相對應的數字值,可以為FPGA協處理器增加能量測量功能。該值也是經過了FPGA的延遲。

作為選擇,JPEG處理可以作為一項獨立的功能通過FPGA來執行,從而使處理器留出更多時間進行數據預處理器。有許多選項可供選擇,但提供一種能夠快速實現不同分割的易用平臺才是至為重要的。

類似的以協處理為本的應用可以從硬件開發平臺的使用中獲得好處。利用硬件平臺可以讓您輕松實驗各種系統和算法分割--將一些功能在FPGA 中實現,而另一些功能放在DSP中。DSP應用程序一般很難用軟件進行仿真,因此快速創建硬件/固件/軟件平臺的能力可以極大地縮短開發時間。使用賽靈思工具套件中的協仿真工具,通過The MathWorks Simulink和目標硬件進行開發,是一種可以大大縮短設計時間的技巧。

圖3:示例系統框圖。

Avnet DSP協處理器設計套件

Avnet DSP協處理設計套件是針對以DSP為導向、同時需要使用FPGA和DSP的廣泛應用開發而設計的。套件配有兩塊主電路板。Virtex-4評估板(如圖4所示)配有 Xilinx Virtex-4 SX-FF668 FPGA、平臺閃速配置PROM、擴展連接器、Cypress CY7C68013 USB2.0 控制器、國家半導體的DP83847 10/100 以太網端口、128x64 OSRAM 圖形顯示器、8MB閃存、32MB DDR SDRAM 以及各種用戶開關和LED。第二塊電路板是 TI DSP 適配器模塊(如圖5所示),用于在Virtex-4 電路板和各種 TI DSP評估板之間起接口作用。可以從 Avnet公司購買TI電路板,完成開發平臺的構建。