隨著集成電路規模迅速擴大,片上系統進入眾核時代。片上眾核系統的主要設計挑戰是什么?如何定義并優化一個片上眾核系統的架構?片上眾核系統如何建模和仿真?片上眾核系統所遭遇到的可靠性問題如何解決?

面對諸多問題,《電子技術應用》在2017年中國(成都)電子展召開之際,特面向西南地區的聽眾,舉辦了“片上眾核系統——演進、仿真及可靠性優化設計”技術沙龍,邀請電子科技大學黃樂天副教授和王君實博士為大家答疑解惑。

片上多核系統技術演進與研究現狀

黃樂天副教授一直從事片上網絡方面的工作,對片上眾核系統有深入的研究,他以“片上多核系統技術演進與研究現狀”為題,首先從片上眾核的誕生和演進入手,對業內兩種不同技術路線演進而來的典型片上網絡架構——CMP架構和MPSoC架構進入詳細的介紹。黃樂天分析了產生兩條不同技術路線的原因:

1 起源不同

· CMP起源于通用并行計算機

· MPSoC起源于嵌入式系統設計

2 任務不同

· 通用計算主要任務是求解大型科學問題——單一算法大數據量

· 嵌入式系統主要任務是完成實時處理和控制——多任務協同

3 開發環境不同

· 通用編程模型——易于編程,易于擴展

· 定制化編程模型——特定目的,定制開發

4 優化目標不同

· 通用計算需要盡量提升數據吞吐率/縮短計算時間

· 嵌入式系統需要保證系統實時性

電子科技大學黃樂天副教授

片上眾核系統的可靠性設計

片上眾核的內部互聯、功耗、存儲機制、可靠性等問題也使片上眾核系統的設計面臨諸多挑戰。王君實博士的演講題目為“集成電路的可靠性設計概述”,他以片上網絡為例,從故障成因、故障類型、故障層次、容錯方法、容錯設計等方面進行了詳細闡述,提出了提高可靠性的設計方法、檢測方法、空間冗余、時間冗余、信息冗余。

電子科技大學王君實博士

自主研發的ESYSim系列片上眾核系統EDA工具

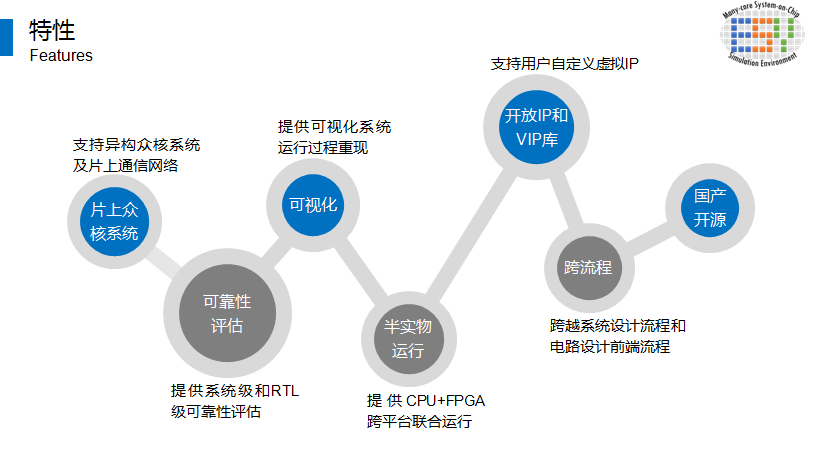

傳統電路設計流程已經不能滿足苛刻的設計指標和設計周期的限制,電子系統級設計ESL設計方法迅速推廣,迫切需要與之配套的EDA仿真工具。國際EDA工具巨頭Synopsys和Mentor分別推出了各自的ESL工具,但仍有缺陷。ESYSim由電子科大ESY碼農隊開發的,是一套國產開源的面向眾核片上系統EDA工具,支持異構眾核系統及片上通信網絡;在系統級和RTL級提供可靠性評估;可視化重現系統運行過程;提供FPGA原型與事務級模型的跨平臺實物聯合運行。

面向眾核片上系統EDA工具——ESYSim的特性

王君實現場以視頻和實物展示的形式演示了ESYSim的設計流程:片上網絡系統級可靠性評估設計、異構多核系統設計與半實物運行、NoC系統設計流程與數字前端設計流程。

意猶未盡

ESYSim EDA工具將亮相“華為杯”第十二屆中國研究生電子設計竟賽,《電子技術應用》祝愿電子科大ESY碼農隊取得好成績!