引言

IDT70V28L(雙口RAM)的存取時間大于20ns,PCI9052工作于25MHz,其存取時間要大于雙口RAM的存取時間。PCI9052是發起交易的主動者,相當于一個慢速器件訪問快速器件,通過可編程器件,可以把PCI9052讀寫控制信號直接傳遞給IDT70V28L,完成時序的匹配。

為將PCI9052的局部邏輯轉換為雙口RAM的讀寫控制信號和地址信號,本設計采用了可編程器件來實現它們之間的接口邏輯電路。在可編程器件設計中,狀態機的設計方法是應用最廣泛的設計方法之一。有限狀態機是一種簡單、結構清晰、設計靈活的方法,它易于建立、理解和維護,特別應用在具有大量狀態轉移和復雜時序控制的系統中,更顯其優勢。鑒于其優勢,本設計采用了Verilog HDL描述的狀態機來實現該接口的時序邏輯,并通過仿真工具驗證了該設計的正確性。

1 PCI9052和雙DRAM

1.1 PCI9052簡介

PCI9052是PLX公司繼PCI9050之后開發的低價位總線目標接口芯片,低功耗,符合PCI2.1規范,它的局部總線(LOCAL BUS)可以通過可編程設置為8/16/32位的(非)復用總線,數據傳輸率可達到132Mb/s。它的主要功能和特性如下:

(1)異步操作。PCI9052的Local Bus與PCI總線的時鐘相互獨立運行,兩總線的異步運行方便了高、低速設備的兼容。Local Bus的運行時鐘頻率范圍為0~40MHz,TTL電平;PCI的運行時鐘頻率范圍0~33MHz。

(2)可編程的局部總線配置。PCI9052支持8位、16位或32位Local Bus,它們可以是復用或非復用。PCI9052有4個字節允許(LBE[3:0]#)信號,26條地址線(LA[27:2]),乖和32位、16位、8位數據線(LAD[3l:0])。

(3)直接從(目標)數據傳送模式。PCI9052支持從PCI總線到Local Bus的猝發存儲器映射空間的傳送和I/O訪問。讀和寫FIFO允許在PCI和局部總線之間的高性能猝發。PCI總線被允許猝發,這樣Local Bus能被設置成猝發或持續單周期。

(4)4個局部片選。PCI9052提供4個片選,每個片選的基地址和范圍被編程成獨立的由SEEPROM或主機。

(5)5個局部地址空間。每個局部地址空間的基地址和范圍被由SEEPROM或主機編程成唯一的。

1.2 雙口RAM

IDT70V28是高速64k×16的雙端口靜態RAM。它能被設計為1024kb的雙端口RAM或者是32位字主從雙端口RAM。該雙口RAM提供兩個獨立的具有控制、地址和I/O引腳的端口。它的主要特性如下:a.可同時訪問雙端口同一存儲器空間;b.高速存儲訪問,訪問速度可達到20ns;c.低功耗運行;d.同過將多個設備級聯,可以方便地將數據線寬擴展到32位或更高;e.具有‘busy’和‘interrupt’旗語。避免訪問沖突:f.可以獨立訪問端口。

2 PCI和雙口RAM之間的接口設計

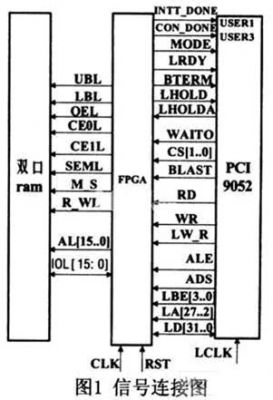

為了解決PCI9052和雙口RAM之間讀寫時序不匹配的問題,采用可編程邏輯器件CYCLONE-II來實現它們之間的接口電路,其信號連接關系如圖1所示。

PCI9052對雙口RAM發出讀寫指令需在FPGA配置完之后,這可以通過查詢CONF_DONE(和USERl相連)和INIT_DONE(和USER3相連)來確定FPGA是否配置完成。如采樣INIT_DONE信號,當其為高,表明FPGA配置完成;如采樣CONF_DONE,當其為高,則PCI9052還需要等待tCD2UM(min=18 μs,max=40 μs)時間后,才能對雙口RAM進行讀寫操作雙口RAM使用的是IDT70V28L,它的存取時間大于20ns。PCI9052采用非復用、單周期讀/寫模式,工作于25MHz時鐘,PCI訪問存儲器是以32位位寬,每讀寫操作一次在Local Bus上都對應2次16位位寬的操作,為了防止相鄰二次交易的沖突,每次狀態機都是以檢測ADS信號有效開始一次讀寫訪問,且插入一個NXDA等待周期。具體讀寫操作實現過程如下。

2.1 PCI9052寫過程

寫過程是用狀態機加以描述,該狀態機有6個狀態,分別是寫空閑、寫開始、寫等待數據、寫過程、寫過程等待和寫結束。具體的狀態轉移圖如圖2所示。

當系統復位后,BTERM、M S被拉高,LHOLD、MODE拉低,寫控制信號無效,狀態機處于寫空閑狀態。

當狀態機處于寫空閑狀態時,在每次上升沿采樣到ADS有效和LW R為高電平,且訪問雙口RAM空間(CS0或CSl有效),狀態機就進入寫開始狀態。在寫開始狀態,狀態機等待未進行一定的操作。接著是寫等待數據狀態,此時根據片選信號CS0和CSl的值譯出SEML、CEOL、CElL,并輸出有效的地址和控制信號R WL、UBL、LBL到雙口RAM。接著是寫過程狀態,為了得到有效的數據,該過程未對輸入輸出操作。然后是寫過程等待狀態,此時,置LRDY信號有效且輸出有效的數據到雙口RAM。最后是寫結束狀態,將片選信號CEOI。、CElL、SEMI。置位無效,在該過程的下一個周期將其余的寫控制信號置為無效,狀態機恢復為寫空閑狀態。

2.2 PCI9052讀過程

讀過程也是用狀態機加以描述,該狀態機有6個狀態,分別是讀空閑、讀開始、讀等待數據、讀過程、讀過程等待和讀結束。其狀態轉移如圖3所示。

當系統復位后,BTERM、M S被拉高,LHOLD、MODE拉低,讀控制信號無效,狀態機處于寫空閑狀態。

當狀態機處于讀空閑狀態時,在每次上升沿采樣到ADS有效和LW R為低電平,且訪問雙口RAM空間(CS0或CSl有效),狀態機轉到讀開始狀態。接著是讀等待數據狀態,此時根據片選信號CS0和CSl的值譯出SEML、CE0L、CElL,并輸出有效的地址和控制信號R WL、UBL、LBL、OEL到雙口RAM。接著是讀過程狀態,為了得到有效的數據,該過程未對輸入輸出操作。然后是讀過程等待狀態,此時,置LRDY信號有效且輸出有效的數據到PCI9052。最后是寫結束狀態,在該過程的下一個周期將讀控制信號置為無效,狀態機恢復為讀空閑狀態。

3 FPGA仿真實現

在Modelsim開發平臺下,實現了PCI9052讀寫雙口RAM的仿真過程,該仿真波形如圖4所示。從仿真波形可以看出該代碼可以實現將PCI90-52的讀寫控制信號轉換成雙口RAM的讀寫控制信號,完成時序的匹配。

4 結語

本設計采用了可編程邏輯芯片來實現PCI訪問雙口RAM的接口電路,該接口電路具有可改性與適用性。隨著微電子技術的發展,可編程器件的容量已經達到千萬門級,越來越多過去必須由專用芯片或器件才能完成的工作現在都可以通過設計軟件由FPGA來實現了。硬件的軟件化已經成為電子行業中不可阻擋的趨勢。