0 引言

近年來,軟件無線電已經成為通信領域一個新的發展方向,數字下變頻技術(DIGItal Down CONverter-DDC)是軟件無線電的核心技術之一,也是計算量最大的部分,一般通過FPGA或專用芯片等硬件實現。

現場可編程門陣列(FPGA)是一種由用戶自行配置的高密度專用數字集成芯片,具有小型化、低功耗、可編程、數字化和快速方便實用的特點。FPGA的靈活性與高速處理的能力,使其由一種靈活的邏輯設計平臺發展為重要的信號處理元件,在各種軟件無線電產品中得到了廣泛的應用。

本文設計和實現了基于FPGA的可編程DDC(DDC),用于寬帶數字中頻軟件無線電接收機中,完成數字下變頻、數據抽取等功能。采用自頂向下的模塊化設計方法,將整個DDC劃分為基本單元,實現這些功能模塊并組成模塊庫。在具體應用時,優化配置各個模塊來滿足具體無線通信系統性能的要求。

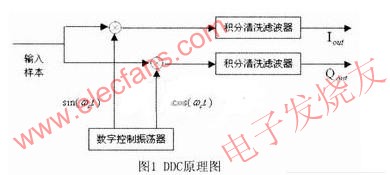

DDC由數控振蕩器(NCO)、數字混頻器和積分清洗濾波器三部分組成,如圖1所示。從原理上比較,DDC和模擬下變頻器是一致的,都是輸入信號與本地振蕩信號混頻,然后經低通濾波器濾除高頻分量,得到基帶信號。

1 DDC的設計

1.1 數控振蕩器的設計

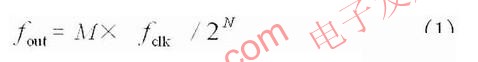

NCO是DDC中的重要組成部分,NCO的目標是產生頻率可變的正交正、余弦樣本信號。NCO產生正弦波樣本通常可采用查表法。即通過輸入的相位數據來尋址查表以輸出相應的正弦波幅值。如圖2所示,碼發生器由相位累加器和查找表構成。累加器按已定的步長進行累加,在每個參考時鐘周期累加,并將結果存入寄存器。當結果溢出時重復執行,累加的過程可以看作NCO輸出頻率的周期。使用查找表選擇相應的SIN和COS值輸出。若使用字長為N位寬的累加器,對于某一頻率控制字A,輸出頻率fout與輸入頻率控制字A的關系為:

其中,fclk為系統時鐘。只要改變控制字A的大小,就可以控制輸出頻率fout。fout變化的最小步長△f由累加器的數據寬度決定。即:

1.2 數字混頻器和積分清洗濾波器的設計及實現

在本設計中,全部過程均采用數字化處理,DDC由一對載波混頻器和一對積分清洗濾波器組成。載波混頻器主要用來實現下變頻,積分清洗濾波器用來去掉高頻分量,數據信息通過監測相鄰兩個符號時間內的相位變化來解調數據。兩路信號在經過積分清洗濾波器后,輸出信號的函數形式仍然不變,只是信號的幅值發生了變化。

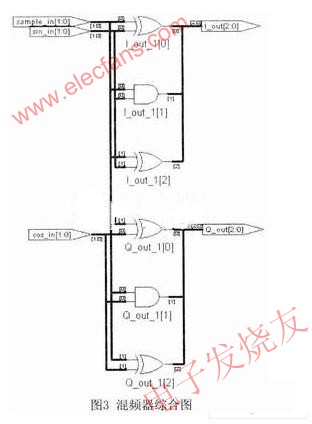

由于利用FPGA設計時,采用的是數字化的解調過程,因此在用VHDL實現時,需要將送過來的基于比特數據類型的位矢量先轉化為有符號數,然后再進行數字運算,運算過程結束后,再將其轉化為位矢量以便于進行信號的傳輸。兩個載波混頻器的輸入信號為前端送來的2比特的采樣數據,取值分別為±1和±3,其中,“00”代表‘1’,“01”代表‘3’,“10”代表‘-1’,“11”代表‘-3’,同樣,本地載波取值±1,±3,這樣經過載波混頻后得到了±1、±3、±9等6個值。將這6個值用三位二進制數表示,高位為符號位,0表示正,1表示負,低位為數據位00、01、10分別代表1、3、9。所以載波混頻器比較簡單,用簡單的門電路就可以實現,圖3為混頻器的綜合圖。對于本系統來說,雖然載波NCO的輸出不是一個方波,但對整體設計沒什么影響。

在實現積分清洗濾波時,采取了前后兩個樣點相加(基于主時鐘mainclk),然后由chip時鐘(chipclk)進行抽樣輸出。這樣做可以回避低通濾波器的同步問題。因為如果采取累加10次(Tchip=10Tmain)然后輸出累加量方式的話,需要準確確定Iout和Qout的chip同步點,這樣才能恢復出正確的基帶信號。因此接收進來的QPSK信號經過下變頻和低通濾波后的波形如圖5中的i out和q out所示。

2 DDC的系統仿真

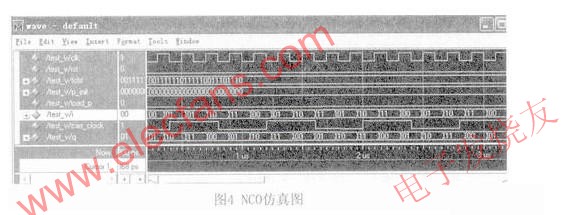

通過VHDL語言編寫NCO模塊,其在Modelsim中的仿真如圖4所示。

其中:clk為基準時鐘信號;i和q分別為sin、cos兩路載波輸出;carr clock為載波周期時鐘,用來記錄載波周期個數;load p為裝載初始相位有效信號;p_init為初始相位值;fctrl為頻率控制字。本設計用的是全局時鐘作為工作時鐘,所以雖然載波NCO的輸出不是一個方波,但對整體設計沒什么影響,本地載波在一個周期內有4個相位,輸出為系統時鐘的分頻信號。

圖5是數字混頻器仿真圖,其中,sAMPle in為接收到的信號,本文中用偽隨機碼;sin in、cos in為輸入的兩路載波信號;i out、q out為輸出結果。

3 結論

本文所設計的簡單DDC系統可以完成基本的下變頻功能,適用于各種需要進行下變頻的場合。并可免去使用專業DDC芯片的麻煩,有效實現所期望的功能。程序設計和實驗表明,將接收進來的經過采樣量化的數字中頻信號進行數字式下變頻在單片FPGA中完成是完全可行的。