摘要:給出了一種基于多相濾波的數字信道化接收機的實現方法,系統的處理帶寬為875 MHz,解決了高速ADC與FPGA" title="FPGA">FPGA處理速度之間的矛盾。為了克服信道化接收機的接收盲區,采用信道重疊的方法,連續覆蓋瞬時帶寬。在信道化處理后接測頻模塊,可以消除虛假信號的輸出和提高測頻精度。整個接收機在單片FPGA中實現,能夠檢測同時到達的兩個信號,并實時輸出脈沖描述字(PDW),經FPGA時序仿真結果驗證了算法模型的正確性和有效性。

信道化接收機是在并行多通道接收機基礎上提出的全概率頻分信道化接收機,它克服了多部接收機并行工作、多通道下變頻等方案具有的設備復雜,各通道性能不一致和可靠性差的缺點。數字信道化接收機具備大的瞬時帶寬、較高的靈敏度、大的動態范圍,能夠檢測和處理同時到達的信號、準確的參數測量能力和一定的信號識別能力。直接信道化接收機的運算量大且輸出速率與采樣速率相同,實現困難,后續處理的壓力很大,高速ADC與慢速信號處理器(FPGA,DSP)是一個“瓶頸”;基于多相濾波的信道化接收機抽取在濾波之前,運算量小,且輸出速率低,便于FPGA實現,這使得在一片FPGA中實現數字信道化成為可能。本文利用信道頻率重疊的方法連續覆蓋整個瞬時帶寬,然后利用Rife算法測頻,根據信道重疊的特點,消除虛假信號。系統帶寬為875 MHz(62.5~937.5 MHz),可以處理兩個同時到達的信號,并實時給出PDW。

1 寬帶數字接收機的結構

1.1 數字信道化原理

信道劃分的基本思想是把信號按頻率均勻地分成D個子頻段(即信道),每個信道的中心頻率為ωk,然后分別移到零中頻,再通過低通濾波器" title="濾波器">濾波器濾出。由于子信道的帶寬遠小于系統瞬時帶寬,因此可以采用抽取的方法來降低信號的輸出速率,降低后續處理的壓力。圖1中,hLP(n)為低通濾波器;M↓表示對經過低通濾波器的信號M倍抽取。對于實信號而言,在偵察接收機中,各信道輸出經過M=D倍抽取后,會產生頻譜混疊,如圖2所示。各個信道的中心頻率為 ,覆蓋整個頻域范圍。但是這種接收機存在信道的虛假輸出。由圖2中可以看出,當輸入信號位于某一信道時,靠近這一信道的相鄰信道會產生虛假輸出。圖2中實線表示實信道,虛線表示鏡像信道。在信道化接收機的輸出端接瞬時測頻模塊,可以消除虛假信號,同時還能提高頻率精度。推導計算出混疊部分頻率的點數,在固定的某一信道,將重疊部分的點只取一次,刪除多余的點數,即消除虛假信號,得到如圖3所示的等效濾波器組。

1.2 實信號無盲區信道化接收機數學模型

由圖1可得第k路信號的輸出為:

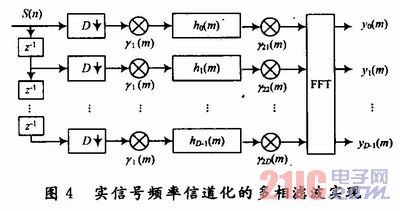

這樣得到實信號數字信道化的多相濾波實現模型如圖4所示。

1.3 算法仿真

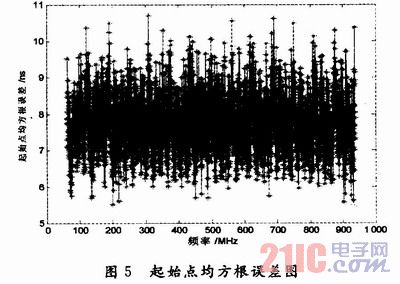

仿真時,設信號的采樣頻率為2 GHz,信道帶寬為62.5 MHz,共16個信道,輸入信噪比為0dB。輸入信號樣本為1 920點(每個信道120點),信號的起始點為112 ns,脈沖寬度為600 ns。在62.5~937.5 MHz間對起始點、脈寬和頻率進行測量,頻率步長為250 kHz,參數的均方根誤差如圖5~圖7所示。

2 寬帶數字接收機的FPGA硬件實現

2.1 系統模塊實現

設計在Xilinx公司的XC4VSX55" title="XC4VSX55">XC4VSX55單片FPGA上實現,包括串并轉換模塊、多相濾波模塊、信號檢測模塊、數據選擇模塊、瞬時測頻模塊以及PDW形成模塊,如圖8所示。

(1)串/并轉換模塊主要功能是降低數據速率,進行并行處理,原始采樣速率為2 000 MSPS,分成D=16路并行數據,每路數據速率變為125 MSPS。

(2)多相濾波模塊的功能是實現高效的多相濾波結構。它由兩級乘法器、有限沖擊響應濾波器(FIR)和16點并行FFT組成。其中,第一級乘法系數隨著數據的先后次序,并按1,1,-1,-1的順序變化來改變相應數據的符號。FIR濾波器采用全并行結構設計,原型低通濾波器的性能見表1。將原型濾波器分成16路,每相濾波器16階。第二級乘法器為一復數乘法。16點全并行FFT,采用流水線結構,可以在一個時鐘節拍內完成FFT運算的功能。

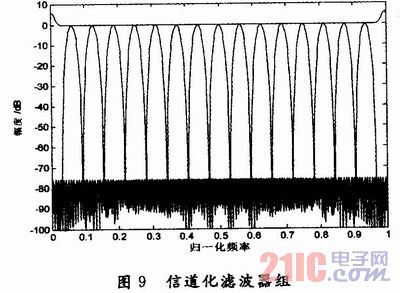

(3)信號檢測模塊的功能是對某一信道是否有信號進行判斷。多相濾波出來的信號為復數,可以對其取模,利用幅度進行門限檢測,同時可以測量到達時間和脈沖寬度。由于濾波器的暫態特性,脈沖信號通過濾波器組會產生“兔耳效應”,為了消除兔耳效應以及噪聲的影響,在每個信道門限檢測的后面加了一個最小脈寬檢測電路,把兔耳效應和噪聲引起的窄脈沖剔除掉,如圖9所示。

(4)數據選擇模塊功能是將有信號信道的數據選出來,為后面的測頻做準備。不必在每個信道后面都接一個測頻模塊以減少后面的測頻模塊,節約芯片資源。

(5)瞬時測頻模塊功能是運用Rife算法估計檢測到信號的瞬時頻率,并消除鏡像信號的影響。根據門限檢測的到達時間,選取N點數據做FFT,左右各刪除N/4點,只取中間的N/2。對這N/2點做Rife插值,若最高譜線大于某固定值時,可以判斷該信道存在真實信號,否則為虛假信號。

(6)脈沖描述字形成模塊是將上述截獲的脈沖信號的到達時間、脈沖寬度和瞬時頻率的參數編碼信息用PDW的形式輸出。

2.2 仿真驗證

經過在ISE中編譯、綜合、布局布線得到FPGA資源使用報告如表2所示;數字信道化接收機實現參數如表3所示。

3 結語

將理論算法和FPGA實現結合起來,分析了數字信道化的原理,提出了一種基于多相濾波的信道化接收機與Rife瞬時測頻相結合的方法。這種方法實現了大帶寬的全概率接收,可以消除虛假信號,同時提高測頻精度。整個接收機在單片FPGA中實現,采用并行和流水線操作,可實現實時檢測,生成脈沖描述字(PDW)。在信道化接收機的數字化、軟件化和小型化發展方面具有重要的現實意義。