對(duì)部隊(duì)中已大量裝備使用的跳擴(kuò)頻電臺(tái)的維護(hù)與測(cè)試需要性能穩(wěn)定的跳擴(kuò)頻信號(hào)" title="跳擴(kuò)頻信號(hào)">跳擴(kuò)頻信號(hào)源,因此非常必要研制使用方便、性能可靠的跳擴(kuò)頻信號(hào)源,以解決部隊(duì)急需,從而提高部隊(duì)的機(jī)務(wù)維修保障能力。隨著電子技術(shù)的發(fā)展,尤其是近十年來(lái)數(shù)字化技術(shù)、超大規(guī)模集成電路和軟件方面的新技術(shù)新成果不斷涌現(xiàn),使得設(shè)計(jì)高可靠、高精度、高穩(wěn)定可攜帶方便的測(cè)試系統(tǒng)成為可能。與傳統(tǒng)測(cè)試系統(tǒng)中的跳擴(kuò)頻信號(hào)源相比,本跳擴(kuò)頻信號(hào)發(fā)送系統(tǒng)采用了FPGA" title="FPGA">FPGA、DDS等多種先進(jìn)技術(shù),具有體積小、重量輕、成本低、集成度高、精度高、可靠性強(qiáng)等優(yōu)點(diǎn),能夠有效地模擬產(chǎn)生需要的跳擴(kuò)頻信號(hào),為機(jī)載跳擴(kuò)頻電臺(tái)的測(cè)試提供可靠的激勵(lì)信號(hào)。

1 系統(tǒng)設(shè)計(jì)總體方案

針對(duì)信號(hào)源需求分析,設(shè)計(jì)系統(tǒng)總體方案如圖1所示。FPGA接收主控單元(MCU)傳遞的信息數(shù)據(jù),接收數(shù)據(jù)源速率為4.8 kb/s。基帶處理部分進(jìn)行差錯(cuò)編碼,編碼處理后的基帶信息數(shù)據(jù)以9.6 kb/s信息速率輸入成幀電路,組幀后信息速率為38.4kb/s。中頻處理電路接收38.4 kb/s信息速率的數(shù)據(jù),并進(jìn)行擴(kuò)頻和DQPSK" title="DQPSK">DQPSK調(diào)制。擴(kuò)頻調(diào)制PN碼碼片速率為1.228 8 M碼片/秒,即每個(gè)調(diào)制符號(hào)對(duì)應(yīng)64個(gè)碼片。系統(tǒng)中頻輸出8.192 MHz DQPSK數(shù)字?jǐn)?shù)據(jù)。系統(tǒng)帶寬跨度為UHF(超短波)105~156 MHz,分了16個(gè)跳頻點(diǎn)帶寬≥45.5MHz。跳頻最小間隔≥2.5 MHz,跳頻速度1 000 Hop/s。

2 關(guān)鍵模塊研究與實(shí)現(xiàn)

2.1 DQPSK調(diào)制

中頻調(diào)制使用數(shù)字化DQPSK(相對(duì)相移鍵控)調(diào)制,該調(diào)制技術(shù)能有效利用數(shù)據(jù)帶寬,同時(shí)采用差分編碼解決QPSK調(diào)制時(shí)出現(xiàn)的相位模糊問題,保證了數(shù)據(jù)的正確解調(diào)。DQPSK調(diào)制框圖如圖2所示。

差錯(cuò)控制編碼采用(217)卷積編碼,碼率為1/2。交織采用塊交織,交織器長(zhǎng)度為384,即一大幀的長(zhǎng)度。為保證數(shù)據(jù)的連續(xù)發(fā)送,交織采用兩個(gè)交織器輪流工作。交織后數(shù)據(jù)以9.6 kb/s交給DQPSK調(diào)制,經(jīng)差分串并轉(zhuǎn)換,以64位碼長(zhǎng)的M序列對(duì)轉(zhuǎn)換后碼率減半的數(shù)據(jù)進(jìn)行擴(kuò)頻調(diào)制和成形濾波。數(shù)控振蕩器(NCO)產(chǎn)生正交調(diào)制的波形,對(duì)成形濾波后的信號(hào)進(jìn)行正交調(diào)制。

2.1.1 濾波成形

DOPSK調(diào)制后的信號(hào)存在以下問題:調(diào)制后的信號(hào)將出現(xiàn)瞬時(shí)變化,這將不可避免地導(dǎo)致信號(hào)的瞬時(shí)頻譜的擴(kuò)散,如果無(wú)失真地傳輸該信號(hào)就要求有很寬的信道帶寬,這在信號(hào)傳輸中是無(wú)法實(shí)現(xiàn),唯一有效的途徑就是采用濾波技術(shù)限制頻譜,這就需要基帶濾波。基帶濾波是在時(shí)域上擴(kuò)展符號(hào),如果設(shè)計(jì)的不好,在接收端將會(huì)引起嚴(yán)重的碼間干擾(ISI)。無(wú)碼間擾準(zhǔn)則可表示為:

![]()

平方根升余弦滾降濾波器有一個(gè)平滑的過(guò)渡帶,通過(guò)引入滾降系數(shù)來(lái)改變傳輸信號(hào)的成形波形,可以減少抽樣定時(shí)脈沖誤差所帶來(lái)的影響。本設(shè)計(jì)中采用56階,滾降系數(shù)為0.35的平方根升余弦濾波器,每個(gè)符號(hào)抽樣8個(gè)點(diǎn)。系統(tǒng)中所設(shè)計(jì)的成形濾波器頻域響應(yīng)如圖3所示。

2.1.2 NCO模塊設(shè)計(jì)

數(shù)控振蕩器NCO可以在高時(shí)鐘頻率下通過(guò)相位累加來(lái)實(shí)現(xiàn),相當(dāng)于一個(gè)給定頻率發(fā)生器產(chǎn)生一個(gè)理想的正弦或余弦波樣本。NCO的輸出頻率可表示為:

![]()

其中,Bθ(n)表示查找表地址的位數(shù),△0表示采樣周期相位增量,fclk是系統(tǒng)時(shí)鐘。

該NCO的設(shè)計(jì)是在FPGA中采用查表法來(lái)實(shí)現(xiàn),它主要由地址累加器和儲(chǔ)存正弦值的ROM表組成。系統(tǒng)時(shí)鐘clk輸入按關(guān)鍵字的步長(zhǎng)累加相位地址,讀出對(duì)應(yīng)ROM中的幅度值。查找表的存儲(chǔ)調(diào)用了ALTERA公司提供的波形數(shù)據(jù)存儲(chǔ)器LPM_ROM文件來(lái)實(shí)現(xiàn)。LPM_ROM是在Quartus II8.0中

使用Mega Winzard Plug-In Manager來(lái)創(chuàng)建定制的。在創(chuàng)建的同時(shí)對(duì)其參數(shù)進(jìn)行初始化設(shè)置,使Quartus II8.O編譯器自動(dòng)地在EP2C8Q208C8芯片中的EAB中實(shí)現(xiàn)ROM函數(shù)的合適部分。設(shè)計(jì)使用了22個(gè)邏輯單元,小于1%,節(jié)省了硬件資源。

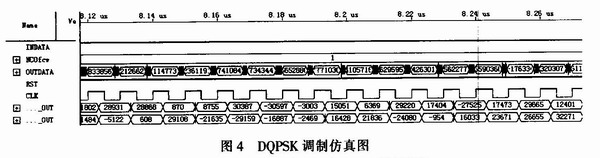

2.1.3 DQPSK的頂層設(shè)計(jì)及仿真

DQPSK頂層模塊主要由3部分組成:差分串并轉(zhuǎn)換、成形濾波和正交調(diào)制。DQPSK調(diào)制仿真結(jié)果如圖4所示。

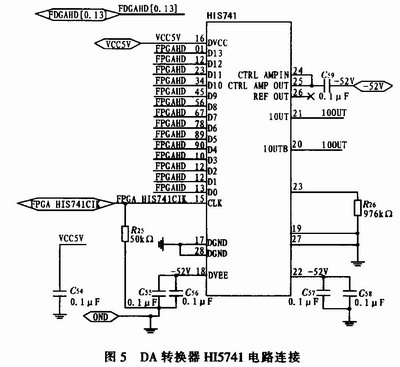

2.2 DA電路設(shè)計(jì)

HI5741是Harris公司生產(chǎn)的電流型14位D/A轉(zhuǎn)換器" title="D/A轉(zhuǎn)換器">D/A轉(zhuǎn)換器,+5 V和-5.2 V操作,最高轉(zhuǎn)換速率可達(dá)100 MHz,輸出信號(hào)為TTL/CMOS電平。轉(zhuǎn)換器提供20.48 mA的滿量程輸出電流并且包含一個(gè)輸出數(shù)據(jù)寄存器和帶隙電壓參考。低靈敏度干擾能量和優(yōu)良的頻域性能。由于HI5741采用了分離結(jié)構(gòu)可以消除由于輸入數(shù)據(jù)不對(duì)稱引起毛刺的脈沖。硬件連接電路如圖5所示。

2.3 跳頻部分設(shè)計(jì)

2.3.1 DDS跳頻碼

DDS輸出頻率一般表達(dá)式![]() ,式中k為頻率碼關(guān)鍵字,fc為時(shí)鐘頻率,而k由下式確定:

,式中k為頻率碼關(guān)鍵字,fc為時(shí)鐘頻率,而k由下式確定:

![]()

式中,A31,A30,…,A1,A0,對(duì)應(yīng)于32位碼值(0或1)。當(dāng)A0=1,其他為0時(shí),則輸出頻率最低,即分辨率:![]() 。當(dāng)A31=1,而A30,…,A1,A0,均為0時(shí)輸出頻率最高:

。當(dāng)A31=1,而A30,…,A1,A0,均為0時(shí)輸出頻率最高:![]() 。在實(shí)際工程中,受到低通濾波器的限制,一般輸出的頻率foutmax≈40%fc。這時(shí)一周期只有兩個(gè)取樣點(diǎn),根據(jù)Nyquist定理已達(dá)到抽樣定理的最小允許值,A31=1,以下碼值只能取0。

。在實(shí)際工程中,受到低通濾波器的限制,一般輸出的頻率foutmax≈40%fc。這時(shí)一周期只有兩個(gè)取樣點(diǎn),根據(jù)Nyquist定理已達(dá)到抽樣定理的最小允許值,A31=1,以下碼值只能取0。

在108~155.975 MHz的帶寬內(nèi),頻率最小間隔大于2.5MHz,將規(guī)定的帶寬分為16個(gè)跳頻點(diǎn),由于在實(shí)際應(yīng)用中,還有一些點(diǎn)的雜散信號(hào)很大,而且離主頻很近,無(wú)法去除。所以應(yīng)該避免輸出這些頻點(diǎn)。這些頻點(diǎn)為靠近fc/3、fc/4、fc/5、fc/6……的頻點(diǎn)。跳頻點(diǎn)數(shù)為16,并基于頻率轉(zhuǎn)換公式![]()

![]() 計(jì)算所對(duì)應(yīng)的32位碼值。

計(jì)算所對(duì)應(yīng)的32位碼值。

2.3.2 跳頻圖案設(shè)計(jì)

跳頻圖案采用對(duì)偶寬間隔跳頻序列,基于m序列,利用非連續(xù)抽頭(L-G)模型,構(gòu)造寬間隔跳頻偽隨機(jī)序列,自相關(guān)性能、互相關(guān)性能較高接近最佳跳頻序列族,提高信號(hào)的抗干擾性。設(shè)計(jì)中基于L-G模型的非連續(xù)抽頭模型,采用本原多項(xiàng)式![]() 設(shè)計(jì)跳頻序列,跳頻碼生成公式如下:

設(shè)計(jì)跳頻序列,跳頻碼生成公式如下:

跳頻序列由FPGA生成并按寬間隔對(duì)偶要求輸出如圖6所示。

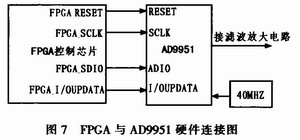

2.3.3 跳頻硬件架構(gòu)

跳頻硬件電路核心是AD9951,硬件連接如圖7所示。該芯片內(nèi)置400MS/s時(shí)鐘,內(nèi)含14位DAC,相位、幅度可編程,有32位頻率控制字、相位偏移字,可用串行I/O控制,采用1.8V電源供電,可4~20倍倍頻,支持大多數(shù)數(shù)字輸入中的5 V輸入電平,可實(shí)現(xiàn)多片同步。通過(guò)送入設(shè)置,送入地址碼和跳頻碼,實(shí)現(xiàn)信號(hào)的跳頻產(chǎn)生。AD9951控制時(shí)序如圖8所示。

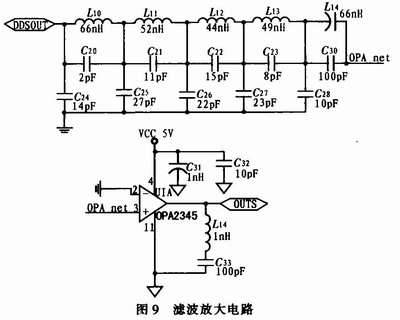

2.3.4 濾波放大電路

針對(duì)相位舍位誤差造成的雜散、幅度量化誤差造成的雜散和DAC非理想特性造成的雜散等3個(gè)主要諧波干擾源。且考慮到濾波緩沖放大電路與已有的DDS的PCB板之間的電路的接口可能會(huì)帶來(lái)較大的干擾,必須對(duì)AD9951輸出頻率進(jìn)行濾波處理。橢圓型濾波器在通帶內(nèi)和阻帶內(nèi)都有等波紋的起伏,比巴特沃斯和切比雪夫有更陡的下降梯度,過(guò)渡帶陡峭,在相同性能指標(biāo)下,橢圓濾波器所需的階數(shù)更小。設(shè)計(jì)借助Mult-isim 10.1高頻電路仿真軟件設(shè)計(jì)了9階橢圓低通濾波電路,截至頻率為160 MHz,通帶內(nèi)的衰減低于0.2 dB。

3 軟件設(shè)計(jì)

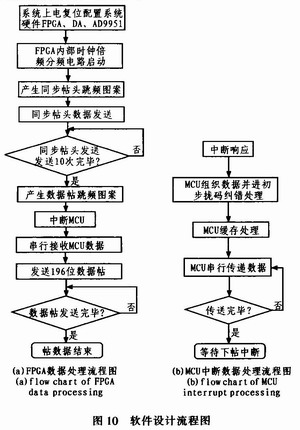

根據(jù)系統(tǒng)需求,采用QuartusⅡ" title="QuartusⅡ">QuartusⅡ8.0開發(fā)平臺(tái),使用VHDL語(yǔ)言編寫FPGA器件執(zhí)行程序,軟件設(shè)計(jì)流程如圖10所示。系統(tǒng)上電復(fù)位,等待MCU啟動(dòng)發(fā)送信號(hào),各個(gè)模塊配置完成,選擇同步發(fā)送時(shí)鐘,等待同步幀頭發(fā)送,同步幀頭以每秒鐘400跳的速率發(fā)送10次,同步幀頭發(fā)送完畢,選擇正常數(shù)據(jù)發(fā)送時(shí)鐘并向MCU產(chǎn)生中斷,從MCU緩存中索取數(shù)據(jù),MCU將數(shù)據(jù)傳遞給FPGA進(jìn)行基帶處理和中頻調(diào)制。

MCU中斷處理,MCU接收FPGA發(fā)出的中斷信號(hào),將迅速響應(yīng)中斷,并組織數(shù)據(jù)為一大幀,進(jìn)行初級(jí)糾錯(cuò)處理后,存入緩存,以備FPGA從MCU緩存中取數(shù)據(jù),保證了中頻調(diào)制數(shù)據(jù)的連續(xù)性。

4 結(jié)束語(yǔ)

依據(jù)跳擴(kuò)頻通信信號(hào)的需求,設(shè)計(jì)了以FPGA和DDS為架構(gòu),用VHDL語(yǔ)言編程實(shí)現(xiàn)的跳擴(kuò)頻信號(hào)發(fā)送系統(tǒng),該系統(tǒng)能以連續(xù)的4.8 Kb/s的速率、在108~155.975 MHz范圍內(nèi)寬間隔跳頻發(fā)送數(shù)據(jù)。本設(shè)計(jì)的主要優(yōu)點(diǎn)是采用了軟件無(wú)線電技術(shù),使用高速、高穩(wěn)定性和高可靠性的集成芯片,體積小重量輕,性價(jià)比高。實(shí)驗(yàn)結(jié)果證明,該跳頻信號(hào)發(fā)送系統(tǒng)可在其外部參數(shù)可控的情況下,穩(wěn)定地傳送全頻段跳頻信號(hào),具有較高的應(yīng)用價(jià)值。