1 引言

隨著社會的發展。使用電梯越來越普遍,已從原來只在商業大廈、賓館過渡到在辦公室、居民樓等多種建筑中,并且對電梯功能的要求也不斷提高,其相應控制方式也在不斷發生變化。電梯的微機化控制主要有:PLC控制、單板機控制、單片機控制、單微機控制、多微機控制和人工智能控制等。隨著EDA技術的快速發展,PLD器件已廣泛應用于電子設計與控制的各個方面。這里使用CPLD器件,采用VHDL語言設計一個16 樓層單個載客箱的電梯控制系統,此控制系統具有使用安全可靠,功能全面的特點,方便人們生活。

2 系統總體設計

該系統采用單片CPLD器件實現一個多樓層單個載客箱的電梯控制器,該控制器可控制電梯完成 16個樓層的載客服務,而且遵循方向優先的原則,能夠提前關電梯門和延遲關電梯門、提供電梯運行的開關控制鍵同時指示電梯運行情況、樓層間的運行時間以及電梯所在樓層的等待時間。根據系統設計要求,并考慮到系統設計的可驗證性,整個系統的輸入、輸出接口設計如圖1所示。

各輸入端口的功能如下:

- CLKIN:基準時鐘信號,為系統提供2 Hz的時鐘脈沖,上升沿有效;

- UPIN:電梯上升請求鍵。由用戶向電梯控制器發出上升請求。高電平有效;

- DOWNIN:電梯下降請求鍵,由用戶向電梯控制器發出下降請求,高電平有效;

- ST_CH[2..0]:樓層選擇鍵人鍵,結合DIRECT完成樓層選擇的鍵入,高電平有效;

- CLOSE:提前關門輸入鍵.可實現無等待時間的提前關門操作,高電平有效;

- DELAY:延遲關門輸入鍵。可實現有等待時間的延遲關門操作,高電平有效;

- RUN STOP:電梯運行或停止開關鍵。可實現由管理員控制電梯的運行或停止,高電平有效。

以下為輸出端口:

- LAMP:電梯運行或等待指示鍵,指示電梯的運行或等待狀況。高電平有效;

- RUN_WAIT[3…0]:電梯運行或等待時間指示鍵,指示電梯運行狀況或等待時間的長短,高電平有效;

- ST_OUT[3…0]:電梯所在樓層指示數碼管,指示電梯當前所在的樓層數。即1~16層,高電平有效;

- DIRECT[3…0]:樓層選擇指示數碼管,指示用戶所要選擇的樓層數,高電平有效。

該設計中,電梯的控制狀態包括運行狀態、停止狀態及等待狀態,其中運行狀態又包含向上和向下狀態。主要動作有開、關門,停靠和啟動。乘客可通過鍵入開、關門按鈕,呼喚按鈕,指定樓層按鈕控制電梯。因此,整個電梯控制器應包括5個組成部分:時序輸出及樓選計數器;電梯服務請求處理器;電梯升降控制器;上升及下降寄存器和電梯次態生成器,圖2為電梯控制器系統框圖。圖3為電梯控制器的內部組成結構。

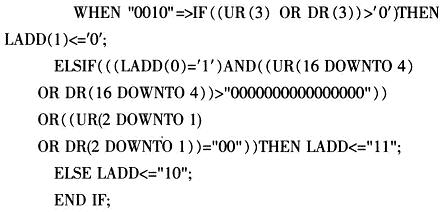

從程序中可以看到,若第3層用戶發送上升/下降請求。則電梯處于等待狀態;若第3層用戶沒有發送上升/下降請求,且4~16層的用戶發送上升,下降請求,或者1.2層的用戶沒有發送任何請求,則電梯處于上升狀態;反之,電梯處于下降狀態。

程序設計中采用方向優先原則,即若電梯處于上升狀態,即使有1,2層用戶發出上升/下降請求,電梯也不響應,而繼續上升,直到響應完所有4~16層用戶的請求后,再下降;反之,若電梯處于下降狀態,即使4~16用戶發出上升/下降請求,電梯也不響應,繼續下降,直到響應完所有用戶的請求后再上升。

(4)P4進程該進程主要完成電梯運行樓層計數及提前/延遲關門控制。

4 VHDL源程序的仿真

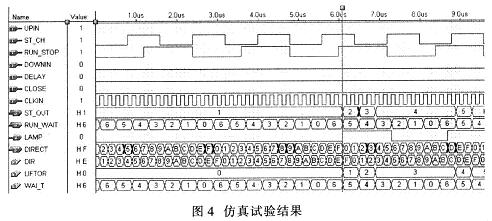

系統程序編寫完畢后,在MAX+pluslI軟件環境下對其編譯仿真。其仿真試驗結果如圖4所示。

圖4中,輸入信號為:UPIN,ST_CH,RUN_STOP,DOWNIN,DELAY,CLOSE和CLKIN;輸出信號為:ST_OUT, RUN_WAIT,LAMP,DIRECT,DIR,LIFTOR和WAI_T。當時鐘上升沿到來時,若WAI_T=0,則它的下一狀態為6;因 DELAY信號始終為低電平,故WAI_T依次自減1計數。RUN_WAIT是WAI_T和0的并置運算,故其值和WAI_T相同。

當時鐘上升沿到來時,DIR進行加1計數,且當DIR=0XF時,DIR的下一狀態值為0。與此同時,DIR加1并賦值給DIRECT。

當LAMP為低電平時,電梯處于等待狀態,故LIFTOR保持其原值不變保持0和3不變;當LAMP為高電平時,電梯處于運行狀態,因UPIN始終為高電平,DOWNIN始終為低電平,故當RUN_STOP為高電平時,電梯只能處于上升狀態,故LIFFOR進行自加1計數,同時,LIFTOR加1賦值給 ST_OUT。

5 硬件實驗

在MAx+plusII軟件編譯完后,采用EPM7128SLC84-6器件下載VHDL源程序,進行硬件試驗。

其下載步驟為:首先,指定采用可編程器件EPM7128SLC84-6;其次,依據輸入、輸出端口指定與之對應的引腳;然后,使用Pof2Jed軟件將編譯后的下載文件*.Pof。轉換成*.Jed文件;最后,使用Atmel ISP軟件將轉換后的*.Jed文件轉換成*.Chn文件。

硬件系統試驗表明,輸出信號的顯示與軟件仿真結果完全相符,達到設計要求。

6 結論

該系統軟件設計中,成功編譯并仿真VHDL源程序,且對仿真圖進行合理分析。在硬件實驗過程中,對VHDL源程序進行成功下載,所得實驗結果與軟件仿真結果完全相符,從而證明電梯運行控制器的設計滿足系統功能要求。